6. Device Configuration¶

This section specifies the objects OSPM uses to configure devices. There are three types of configuration objects:

Device identification objects associate platform devices with Plug and Play IDs.

Device configuration objects declare and configure hardware resources and characteristics for devices enumerated via ACPI.

Device insertion and removal objects provide mechanisms for handling dynamic insertion and removal of devices.

There are two types of Device objects:

A Full Device Descriptor, which contains the complete description of a devices that cannot be discovered through any other standard Bus enumeration mechanism. This type of Device object is enumerated by the ACPI subsystem (OSPM), and contains a Hardware ID object (_HID).

An Agumented Device Descriptor, which contains additional device information that is not provided from the Device itself, yet is needed by the Device or Bus driver in order to properly configure and use the device. This type of device is enumerated by a bus-specific enumeration mechanism, and OSPM uses the Address (_ADR) to match the ACPI Device object in the Namespace to the device discovered through bus enumeration.

This section also defines the ACPI device-resource descriptor formats. Device-resource descriptors are used as parameters by some of the device configuration objects.

6.1. Device Identification Objects¶

Device identification objects associate each platform device with a Plug and Play device ID for each device. All the device identification objects are listed in the table below:

Object |

Description |

|---|---|

_ADR |

Object that evaluates to a device’s address on its parent bus. |

_CID |

Object that evaluates to a device’s Plug and Play-compatible ID list. |

_CLS |

Object that evaluates to a package of coded device-class information. |

_DDN |

Object that associates a logical software name (for example, COM1) with a device. |

_HID |

Object that evaluates to a device’s Plug and Play hardware ID. |

_HRV |

Object that evaluates to an integer hardware revision number. |

_MLS |

Object that provides a human readable description of a device in multiple languages. |

_PLD |

Object that provides physical location description information. |

_SUB |

Object that evaluates to a device’s Plug and Play subsystem ID. |

_SUN |

Object that evaluates to the slot-unique ID number for a slot. |

_STR |

Object that contains a Unicode identifier for a device. Can also be used for thermal zones. |

_UID |

Object that specifies a device’s unique persistent ID, or a control method that generates it. |

For any device that is on a non-enumerable type of bus (for example, an ISA bus), OSPM enumerates the devices’ identifier(s) and the ACPI system firmware must supply an _HID object (plus one or more optional objects such as _CID, _CLS, _HRV, _SUB) for each device to enable OSPM to do that. For devices on an enumerable type of bus, such as a PCI bus, the ACPI system must identify which device on the enumerable bus is identified by a particular address; the ACPI system firmware must supply an _ADR object for each device to enable this. A device object must contain either an _HID object or an _ADR object, but must not contain both.

If any of these objects are implemented as control methods, these methods may depend on operation regions. Since the control methods may be evaluated before an operation region provider becomes available, the control method must be structured to execute in the absence of the operation region provider. (_REG methods notify the platform runtime firmware of the presence of operation region providers.) When a control method cannot determine the current state of the hardware due to a lack of operation region provider, it is recommended that the control method should return the condition that was true at the time that control passed from the platform boot firmware to the OS. (The control method should return a default, boot value).

6.1.1. _ADR (Address)¶

This object is used to supply OSPM with the address of a device on its parent bus. An _ADR object must be used when specifying the address of any device on a bus that has a standard enumeration algorithm (see Configuration and “Plug and Play”, for the situations when these devices do appear in the ACPI namespace). The _ADR object is valid only within an Augmented Device Descriptor.

Arguments:

None

Return Value:

An Integer containing the address of the device

An _ADR object can be used to provide capabilities to the specified address even if a device is not present. This allows the system to provide capabilities to a slot on the parent bus.

OSPM infers the parent bus and segment from the location of the _ADR object’s device package in the ACPI namespace. For more information about the positioning of device packages in the ACPI namespace, see Device (Declare Device Package)

_ADR object information must be static and can be defined for the following bus types listed in ADR Object Address Encodings.

BUS |

Address Encoding |

|---|---|

EISA |

EISA slot number 0-F |

Floppy Bus |

Drive select values used for programming the floppy controller to access the specified INT13 unit number. The _ADR Objects should be sorted based on drive select encoding from 0-3. |

I3C |

Bits [63:52] - Reserved Bits [51:48] - Master Instance Bits [47:0] - I3C Device Provisional ID, following encoding defined in the MIPI Specification for I3C. If an I3C device supports a static address instead of a Provisional ID, then bits [47:7] are Reserved (zero), and bits [6:0] are the 7-bit static address. |

IDE Controller |

0-Primary Channel, 1-Secondary Channel |

IDE Channel |

0-Master drive, 1-Slave drive |

Intel® High Definition Audio |

High word - SDI (Serial Data In) ID of the codec that contains the function group. Low word - Node ID of the function group. |

PCI |

High word-Device #, Low word-Function #. (for example, device 3, function 2 is 0x00030002). To refer to all the functions on a device #, use a function number of FFFF). |

PCMCIA |

Socket #; 0-First Socket |

PC CARD |

Socket #; 0-First Socket |

Serial ATA |

SATA Port: High word–Root port #, Low word–port number off of a SATA port multiplier, or 0xFFFF if no port multiplier attached. (For example, root port 2 would be 0x0002FFFF. If instead a port multiplier had been attached to root port 2, the ports connected to the multiplier would be encoded 0x00020000, 0x00020001, etc.) The value 0xFFFFFFFF is reserved. |

SMBus |

Lowest Slave Address |

USB Root HUB |

Only one child of the host controller. It must have an _ADR of 0. No other children or values of _ADR are allowed. |

USB Ports |

Port number (1-n) |

SDIO Bus |

High word - Slot number (0-First Slot) Low word - Function number (see SD specification for definitions.) |

NVDIMM |

NFIT Device handle as defined by the NVDIMM Region Mapping Structure |

6.1.2. _CID (Compatible ID)¶

This optional object is used to supply OSPM with a device’s Plug and Play-Compatible Device ID. Use _CID objects when a device has no other defined hardware standard method to report its compatible IDs. The _CID object is valid only within a Full Device Descriptor. An _HID object must also be present.

Arguments:

None

Return Value:

An Integer or String containing a single CID or a Package containing a list of CIDs

A _CID object evaluates to either:

A single Compatible Device ID

A package of Compatible Device IDs for the device – in the order of preference, highest preference first.

Each Compatible Device ID must be either:

A valid HID value (a 32-bit compressed EISA type ID or a string such as “ACPI0004”).

A string that uses a bus-specific nomenclature. For example, _CID can be used to specify the PCI ID. The format of a PCI ID string is one of the following:

"PCI\CC_ccss" "PCI\CC_ccsspp" "PCI\VEN_vvvv&DEV_dddd&SUBSYS_ssssssss&REV_rr" "PCI\VEN_vvvv&DEV_dddd&SUBSYS_ssssssss" "PCI\VEN_vvvv&DEV_dddd&REV_rr" "PCI\VEN_vvvv&DEV_dddd"Where:

cc - hexadecimal representation of the Class Code byte ss - hexadecimal representation of the Subclass Code byte pp - hexadecimal representation of the Programming Interface byte vvvv - hexadecimal representation of the Vendor ID dddd - hexadecimal representation of the Device ID ssssssss - hexadecimal representation of the Subsystem ID rr - hexadecimal representation of the Revision byte

A compatible ID retrieved from a _CID object is only meaningful if it is a non-NULL value.

Example ASL:

Device (XYZ) {

Name (_HID, EISAID ("PNP0303")) // PC Keyboard Controller

Name (_CID, EISAID ("PNP030B"))

}

6.1.3. _CLS (Class Code)¶

This object is used to supply OSPM with the PCI-defined base-class, sub-class and programming interface for a device. This object is optional. However, it may be useful for loading generic drivers on hardware that is compatible with PCI -defined device classes, but that is not implemented on the PCI bus (and is therefore enumerated by ACPI.)

Arguments:

None

Return Value:

A Package containing the PCI -defined class information as a list of Integers:

Package(3) {<base-class code>, <sub-class code>, <Programming Interface code>}

A list of available class codes and programming interface codes is provided by the PCI SIG. See “PCI Code and ID Assignment Specification”, available from “Links to ACPI-Related Documents” (http://uefi.org/acpi ) under the heading “PCI Code and ID Assignment Specification

Example ASL:

Device(SATA) //AHCI- compatible SATA controller

{

Name(_HID, "...")

Name(_CLS, Package (3)

{

0x01, // Base Class (01h == Mass Storage)

0x06, // Sub-Class (06h == SATA)

0x01, // Programming Interface (01h == AHCI)

})

Name(_CRS, ResourceTemplate()

{

... // AHCI-defined system resources

})

}

6.1.4. _DDN (DOS Device Name)¶

This object is used to associate a logical name (for example, COM1) with a device. This name can be used by applications to connect to the device.

Arguments:

None

Return Value:

A String containing the DOS device name

6.1.5. _HID (Hardware ID)¶

This object is used to supply OSPM with the device’s PNP ID or ACPI ID.

See also

PNP ID and ACPI ID Registry is at http://www.uefi.org/PNP_ACPI_Registry .

When describing a platform, use of any _HID objects is optional. However, a _HID object must be used to describe any device that will be enumerated by OSPM. OSPM only enumerates a device when no bus enumerator can detect the device ID. For example, devices on an ISA bus are enumerated by OSPM. Use the _ADR object to describe devices enumerated by bus enumerators other than OSPM. The _HID object is valid only within a Full Device Descriptor.

Arguments:

None

Return Value:

An Integer or String containing the HID

A _HID object evaluates to either a numeric 32-bit compressed EISA type ID or a string. If a string, the format must be an alphanumeric PNP or ACPI ID with no asterisk or other leading characters.

A valid PNP ID must be of the form “AAA####” where A is an uppercase letter and # is a hex digit. A valid ACPI ID must be of the form “NNNN####” where N is an uppercase letter or a digit (‘0’-‘9’) and # is a hex digit. This specification reserves the string “ACPI” for use only with devices defined herein. It further reserves all strings representing 4 HEX digits for exclusive use with PCI-assigned Vendor IDs.

Example ASL:

Name (_HID, EISAID ("PNP0C0C")) // Control-Method Power Button

Name (_HID, EISAID ("INT0800")) // Firmware Hub

Name (_HID, "ACPI0003") // AC adapter device

Name (_HID, "MSFT0003") // Vendor-defined device

Name (_HID, "80860003") // PCI-assigned device identifier

6.1.6. _HRV (Hardware Revision)¶

This object is used to supply OSPM with the device’s hardware revision. The use of _HRV is optional.

Arguments:

None

Return Value:

An Integer (DWORD) containing the hardware revision number

Example ASL:

Name (_HRV, 0x0003) // Revision number 3 of this hardware device

6.1.7. _MLS (Multiple Language String)¶

The _MLS object provides OSPM a human readable description of a device in multiple languages. This information may be provided to the end user when the OSPM is unable to get any other information about this device. Although this functionality is also provided by the _STR object, _MLS expands that functionality and provides vendors with the capability to provide multiple strings in multiple languages. The _MLS object evaluates to a package of packages. Each sub-package consists of a Language identifier and corresponding unicode string for a given locale. Specifying a language identifier allows OSPM to easily determine if support for displaying the Unicode string is available. OSPM can use this information to determine whether or not to display the device string, or which string is appropriate for a user’s preferred locale.

It is assumed that OSPM will always support the primary English locale to accommodate English embedded in a non-English string, such as a brand name.

If OSPM doesn’t support the specific sub-language ID it may choose to use the primary language ID for displaying device text.

Arguments:

None

Return Value:

A variable-length Package containing a list of language descriptor Packages as described below.

Return Value Information:

Package {

LanguageDescriptor[0] // Package

LanguageDescriptor[n] // Package

}

Each Language Descriptor sub-Package contains the elements described below:

Package {

LanguageId // String

UnicodeDescription // Buffer

}

LanguageId is a string identifying the language. This string follows the format specified in the Internet RFC 3066 document (Tags for the Identification of Languages). In addition to supporting the existing strings in RFC 3066, the table below lists aliases that are also supported.

RFC String |

Supported Alias String |

|---|---|

zh-Hans |

zh-chs |

zh-Hant |

zh-cht |

UnicodeDescription is a Buffer containing a Unicode (UTF-16) string. This string contains the language-specific description of the device corresponding to the LanguageID. The Unicode() ASL macro can be used to create this Buffer.

Example:

Device (XYZ) {

Name (_ADR, 0x00020001)

Name ( \_MLS, Package(){(2){"en", Unicode("ACME super DVD controller")}})

}

6.1.8. _PLD (Physical Location of Device)¶

This optional object is a method that conveys to OSPM a general description of the physical location of a device’s external connection point. The _PLD may be child object for any ACPI Namespace object the system wants to describe. This information can be used by system software to describe to the user which specific connector or device input mechanism may be used for a given task or may need user intervention for correct operation. The _PLD should only be evaluated when its parent device is present as indicated by the device’s presence mechanism (i.e. _STA or other)

An externally exposed device connection point can reside on any surface of a system’s housing. The respective surfaces of a system’s housing are identified by the “Panel” field (described below). The _PLD method returns data to describe the location of where the device’s connection point resides and a Shape (described below) that may be rendered at that position. One physical device may have several connection points. A _PLD describes the offset and rotation of a single device connection point from an “origin” that resides in the lower left hand corner of its Panel.

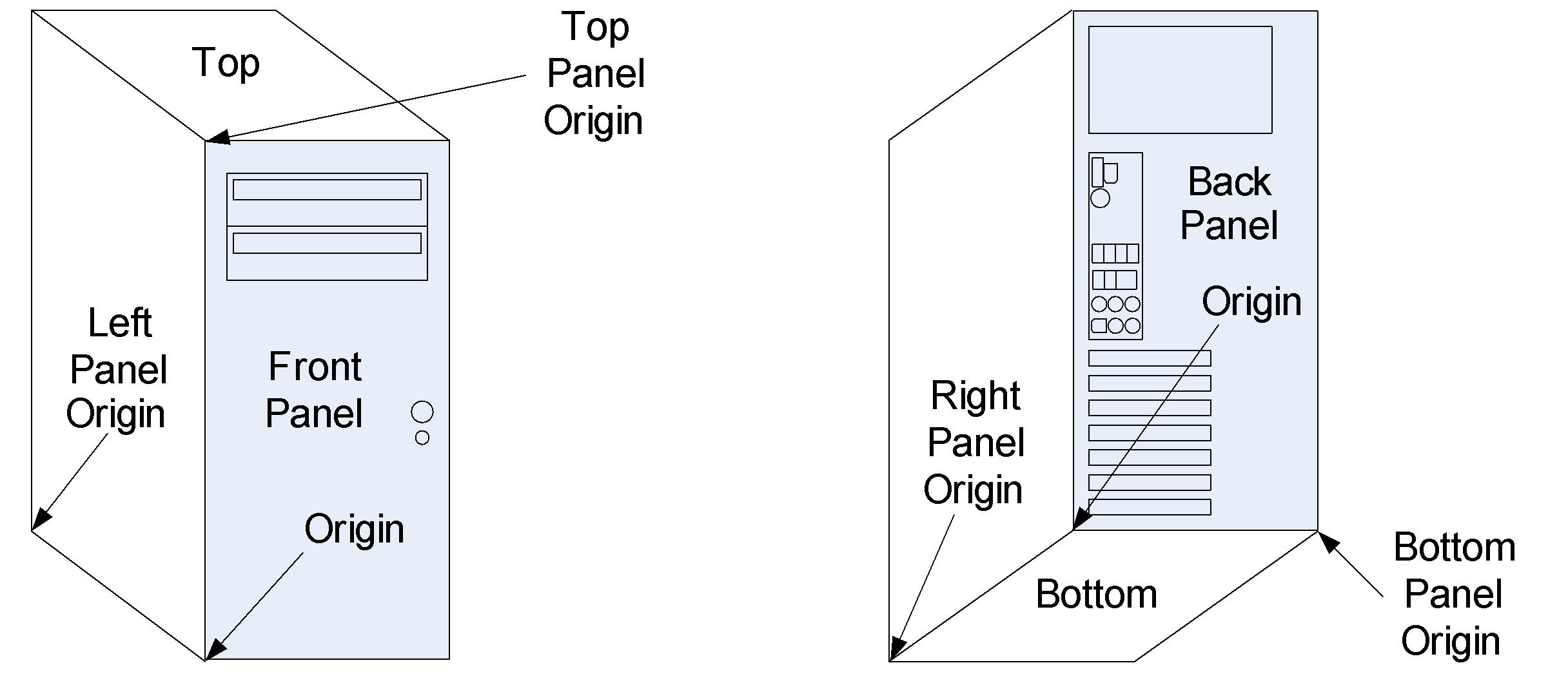

All Panel references (Top, Bottom, Right, Left, etc.) are interpreted as though the user is facing the front of the system. For handheld mobile devices, the front panel is the one holding the display screen, and its origin is in the lower-left corner when the display is viewed in the Portrait orientation. For example, the Right Panel is the right side of the system as viewed from the front.

All “origin” references for a Panel are interpreted as its lower left corner when the user is facing the respective Panel. The Top Panel shall be viewed with the system is viewed resting on its Front Panel, and the Bottom Panel shall be viewed with the system resting on its Back Panel. All other Panels shall be viewed with the system resting on its Bottom Panel. See System Panel and Panel Origin Positions for more information.

Fig. 6.1 System Panel and Panel Origin Positions¶

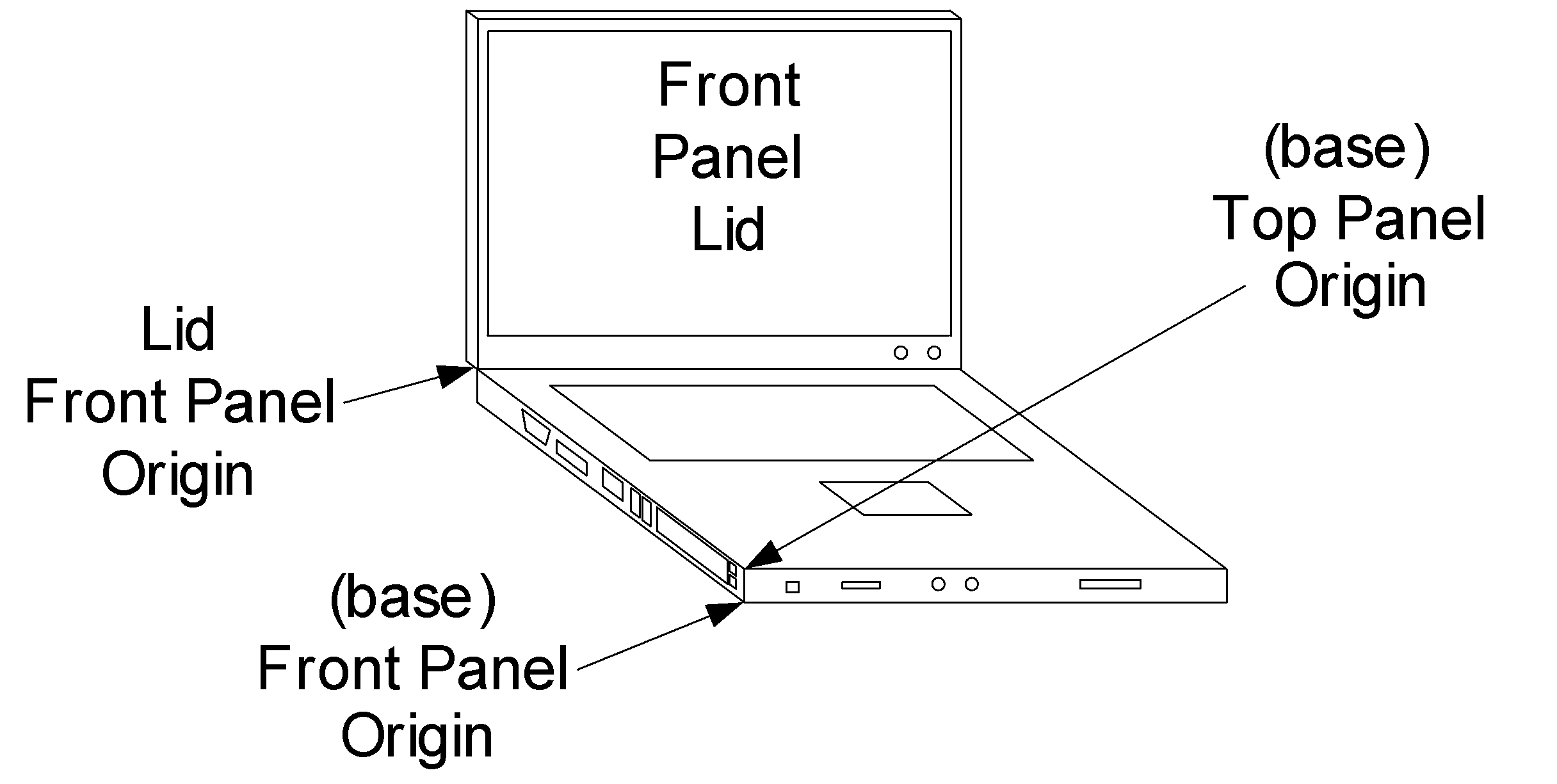

The data bits also assume that if the system is capable of opening up like a laptop that the device may exist on the base of the laptop system or on the lid. In the case of the latter, the “Lid” bit (described below) should be set indicating the device connection point is on the lid. If the device is on the lid, the description describes the device’s connection point location when the system is opened with the lid up. If the device connection point is not on the lid, then the description describes the device’s connection point location when the system with the lid closed.

Fig. 6.2 Laptop Panel and Panel Origin Positions¶

To render a view of a system Panel, all _PLDs that define the same Panel and Lid values are collected. The _PLDs are then sorted by the value of their Order field and the view of the panel is rendered by drawing the shapes of each connection point (in their correct Shape, Color, Horizontal Offset, Vertical Offset, Width, Height, and Orientation) starting with all Order = 0 _PLDs first. Refer to PLD Back Panel Rendering for an example.

The location of a device connection point may change as a result of the system connecting or disconnecting to a docking station or a port replicator. As such, Notify event of type 0x09 will cause OSPM to re-evaluate the _PLD object residing under the particular device notified. If a platform is unable to detect the change of connecting or disconnecting to a docking station or port replicator, a _PLD object should not be used to describe the device connection points that will change location after such an event.

Arguments:

None

Return Value:

A variable-length Package containing a list of Buffers

This method returns a package containing a single or multiple buffer entries. At least one buffer entry must be returned using the bit definitions below.

Name |

Definition |

DWORD |

Bit Offset (DWORD) |

Bit Offset (Buffer) |

Length (bits) |

|---|---|---|---|---|---|

Revision |

The current Revision is 0x2 |

0 |

0 |

0 |

7 |

Ignore Color |

If this bit is set, the Color field is ignored, as the color is unknown. |

0 |

7 |

7 |

1 |

Color |

24-bit RGB value for the color of the device connection point:

Bits [15:8]=red value

Bits [23:16]=green value

Bits [31:24]=blue value

|

0 |

8 |

8 |

24 |

Width |

Width of the widest point of the device connection point, in millimeters |

1 |

0 |

32 |

16 |

Height |

Height of the tallest point of the device connection point, in millimeters |

1 |

16 |

48 |

16 |

User Visible |

Set if the device connection point can be seen by the user without disassembly. |

2 |

0 |

64 |

1 |

Dock |

Set if the device connection point resides in a docking station or port replicator. |

2 |

65 |

1 |

|

Lid |

Set if this device connection point resides on the lid of laptop system. |

2 |

66 |

1 |

|

Panel |

Describes which panel surface of the system’s housing the device connection point resides on:

0 - Top

1 - Bottom

2 - Left

3 - Right

4 - Front

5 - Back

6 - Unknown (Vertical Position and Horizontal Position will be ignored)

|

2 |

67 |

3 |

|

Vertical Position on the panel where the device connection point resides |

0 - Upper

1 - Center

2 - Lower

|

2 |

70 |

2 |

|

Horizontal Position on the panel where the device connection point resides. |

2 |

72 |

2 |

||

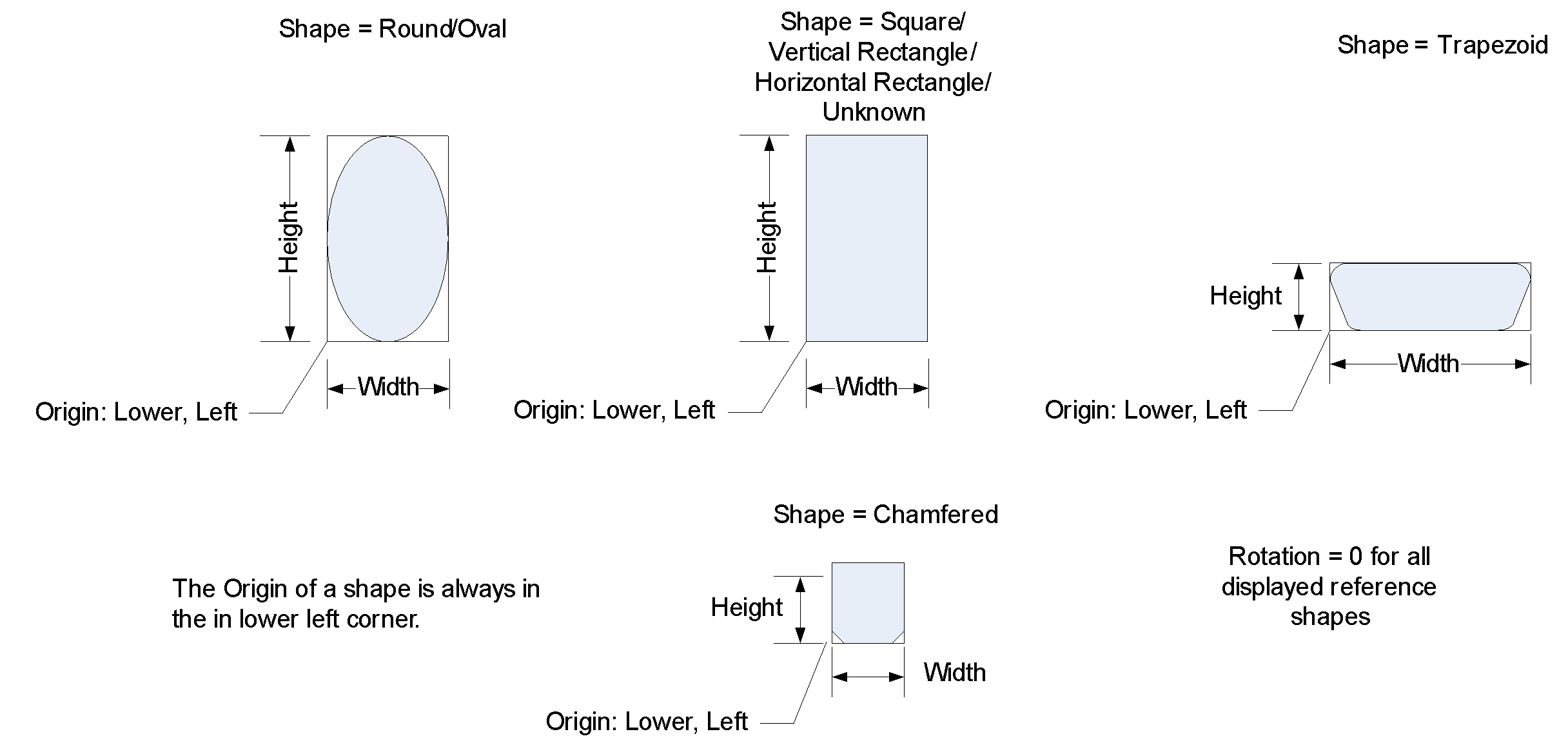

Shape |

Describes the shape of the device connection point. The Width and Height fields may be used to distort a shape, e.g. A Round shape will look like an Oval shape if the Width and Height are not equal. And a Vertical Rectangle or Horizontal Rectangle may look like a square if Width and Height are equal. See Default Shape Definitions:

0 - Round

1 - Oval

2 - Square

3 - Vertical Rectangle

4 - Horizontal Rectangle

5 - Vertical Trapezoid

6 - Horizontal Trapezoid

7 - Unknown - Shape rendered as a Rectangle with dotted lines

8 - Chamfered

15:9 - Reserved

|

2 |

74 |

4 |

|

Group Orientation |

if Set, indicates vertical grouping, otherwise horizontal is assumed. |

2 |

78 |

1 |

|

Group Token |

Unique numerical value identifying a group. |

2 |

79 |

1 |

|

Group Position |

Identifies this device connection point’s position in the group (i.e. 1st, 2nd) |

2 |

87 |

8 |

|

Bay |

Set if describing a device in a bay or if device connection point is a bay. |

2 |

95 |

1 |

|

Ejectable |

Set if the device is ejectable. Indicates ejectability in the absence of _EJx objects. |

2 |

96 |

1 |

|

OSPM Ejection required |

OSPM Ejection required: Set if OSPM needs to be involved with ejection process. User-operated physical hardware ejection is not possible. |

2 |

97 |

1 |

|

Cabinet Number |

For single cabinet system, this field is always 0. |

2 |

98 |

8 |

|

Card Cage Number |

For single card cage system, this field is always 0. |

2 |

106 |

8 |

|

Reference |

if Set, this _PLD defines a “reference” shape that is used to help orient the user with respect to the other shapes when rendering _PLDs. |

2 |

114 |

1 |

|

Rotation |

Rotates the Shape clockwise in 45 degree steps around its origin where:

0 - 0°

1 - 45°

2 - 90°

3 - 135°

4 - 180°

5 - 225°

6 - 270°

7 - 315°

|

2 |

115 |

4 |

|

Order |

Identifies the drawing order of the connection point described by a _PLD:

Order = 0 connection points are drawn before Order = 1 connection points.

Order = 1 before Order = 2, and so on.

Order = 31 connection points are drawn last.

Order should always start at 0 and be consecutively assigned.

|

2 |

119 |

5 |

|

Reserved |

Reserved, must contain a value of 0. |

2 |

124 |

4 |

|

Vertical Offset |

Offset of Shape Origin from Panel Origin (in mm). A value of 0xFFFFFFFF indicates that this field is not supplied. |

2 |

128 |

16 |

|

Horizontal Offset |

Offset of Shape Origin from Panel Origin (in mm). A value of 0xFFFFFFFF indicates that this field is not supplied. |

2 |

144 |

16 |

Note

All additional buffer entries returned may contain OEM-specific data, but must begin in a {GUID, data} pair. These additional data may provide complimentary physical location information specific to certain systems or class of machines.

Fig. 6.3 Default Shape Definitions¶

Buffers 1–N Return Value (Optional):

Buffer 1 Bit [127:0] - GUID 1

Buffer 2 Bit [127:0] - Data 1

Buffer 3 Bit [127:0] - GUID 2

Buffer 4 Bit [127:0] - Data 2

etc.

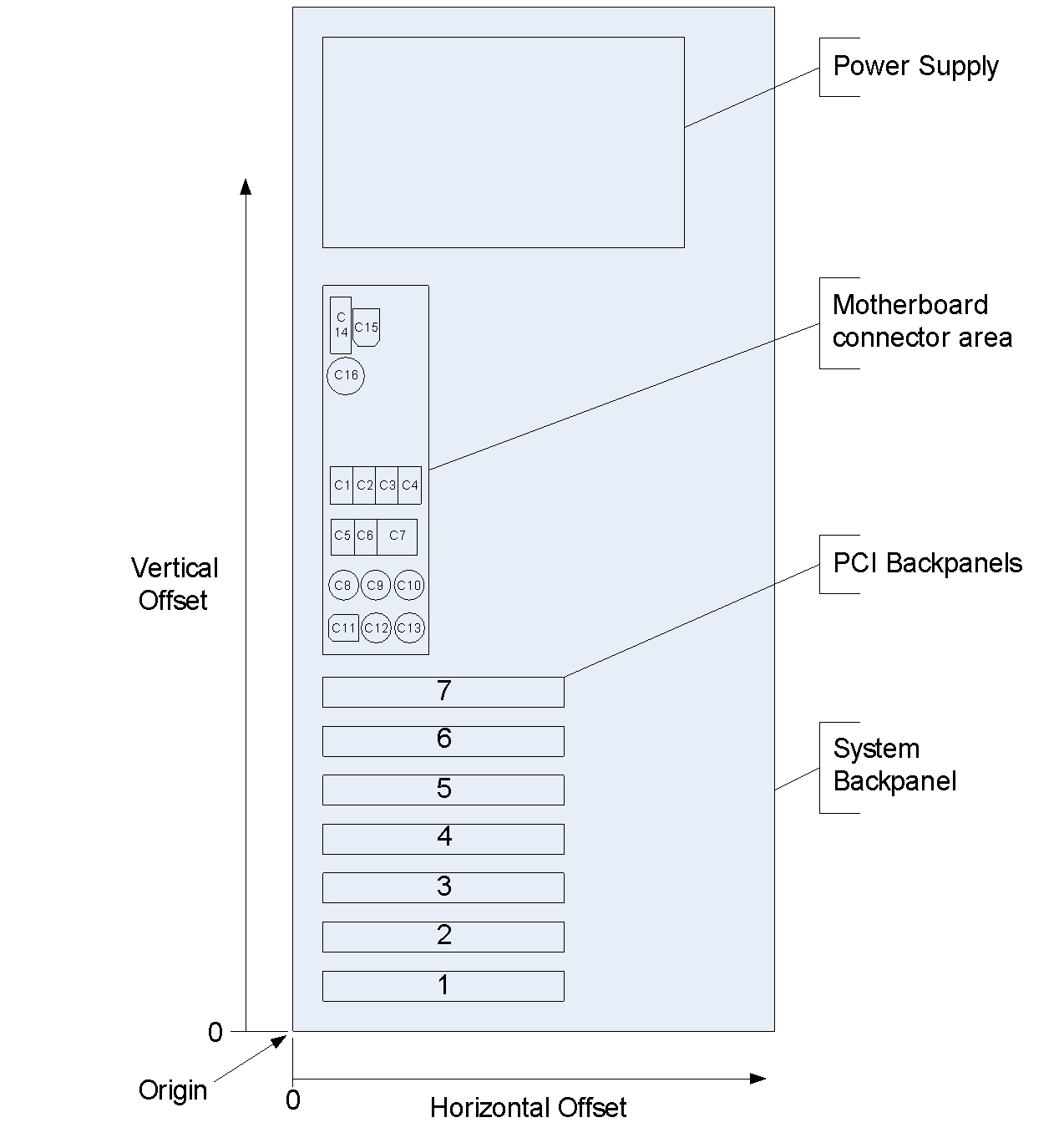

PLD Back Panel Rendering provides an example of a rendering of the external device connection points that may be conveyed to the user by _PLD information. Note that three _PLDs (System Back Panel, Power Supply, and Motherboard (MB) Connector Area) that are associated with the System Bus tree (_SB) object. Their Reference flag is set indicating that are used to provide the user with visual queues for identifying the relative locations of the other device connection points.

The connection points (C1 through C16) are defined by _PLD objects found in the System bus tree.

The following connection points all have their Panel and Lid fields set to Back and 0, respectively. And the Reference flag of the System Back Panel, Power Supply, and MB Connector Area connection points are set to 1. in this example are used to render PLD Back Panel Rendering:

Name |

Ignore Color |

R |

G |

B |

Width |

Height |

VOff |

HOff |

Shape |

Notation |

Goup Position |

Rotation |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

Back Panel |

Yes |

0 |

0 |

0 |

2032 |

4318 |

0 |

0 |

V Rect |

1 |

0 |

|

MB Conn area |

Yes |

0 |

0 |

0 |

445 |

1556 |

1588 |

127 |

V Rect |

2 |

0 |

|

Power Supply |

Yes |

0 |

0 |

0 |

1524 |

889 |

3302 |

127 |

H Rect |

2 |

0 |

|

USB Port 1 |

No |

0 |

0 |

0 |

125 |

52 |

2223 |

159 |

H Rect |

C1 |

3 |

90 |

USB Port 2 |

No |

0 |

0 |

0 |

125 |

52 |

2223 |

254 |

H Rect |

C2 |

3 |

90 |

USB Port 3 |

No |

0 |

0 |

0 |

125 |

52 |

2223 |

350 |

H Rect |

C3 |

3 |

90 |

USB Port 4 |

No |

0 |

0 |

0 |

125 |

52 |

2223 |

445 |

H Rect |

C4 |

3 |

90 |

USB Port 5 |

No |

0 |

0 |

0 |

125 |

52 |

2007 |

159 |

H Rect |

C5 |

3 |

90 |

USB Port 6 |

No |

0 |

0 |

0 |

125 |

52 |

2007 |

254 |

H Rect |

C6 |

3 |

90 |

Ethernet |

No |

0 |

0 |

0 |

157 |

171 |

2007 |

350 |

V Rect |

C7 |

3 |

90 |

Audio 1 |

No |

FF |

FF |

FF |

127 |

127 |

1945 |

151 |

Round |

C8 |

3 |

90 |

Audio 2 |

No |

151 |

247 |

127 |

127 |

127 |

1945 |

286 |

Round |

C9 |

3 |

90 |

Audio 3 |

No |

0 |

0 |

0 |

127 |

127 |

1945 |

427 |

Round |

C10 |

3 |

90 |

SPDIF |

No |

0 |

0 |

0 |

112 |

126 |

1756 |

176 |

V Trap |

C11 |

3 |

90 |

Audio 4 |

No |

0 |

FF |

0 |

127 |

127 |

1765 |

288 |

Round |

C12 |

3 |

90 |

Audio 5 |

No |

0 |

0 |

FF |

127 |

127 |

1765 |

429 |

Round |

C13 |

3 |

90 |

SATA |

No |

0 |

0 |

0 |

239 |

88 |

3091 |

159 |

H Rect |

C14 |

3 |

90 |

1394 |

No |

0 |

0 |

0 |

112 |

159 |

2890 |

254 |

H Trap |

C15 |

3 |

0 |

Coax |

No |

0 |

0 |

0 |

159 |

159 |

2842 |

143 |

Round |

C16 |

3 |

90 |

PCI 1 |

No |

0 |

0 |

0 |

1016 |

127 |

127 |

127 |

H Rect |

1 |

3 |

0 |

PCI 2 |

No |

0 |

0 |

0 |

1016 |

127 |

334 |

127 |

H Rect |

2 |

3 |

0 |

PCI 3 |

No |

0 |

0 |

0 |

1016 |

127 |

540 |

127 |

H Rect |

3 |

3 |

0 |

PCI 4 |

No |

0 |

0 |

0 |

1016 |

127 |

747 |

127 |

H Rect |

4 |

3 |

0 |

PCI 5 |

No |

0 |

0 |

0 |

1016 |

127 |

953 |

127 |

H Rect |

5 |

3 |

0 |

PCI 6 |

No |

0 |

0 |

0 |

1016 |

127 |

1159 |

127 |

H Rect |

6 |

3 |

0 |

PCI 7 |

No |

0 |

0 |

0 |

1016 |

127 |

1366 |

127 |

H Rect |

7 |

3 |

0 |

Note that the origin is in the lower left hand corner of the Back Panel, where positive Horizontal and Vertical Offset values are to the right and up, respectively.

Fig. 6.4 PLD Back Panel Rendering¶

6.1.9. _SUB (Subsystem ID)¶

This object is used to supply OSPM with the device’s Subsystem ID. The use of _SUB is optional.

Arguments:

None

Return Value:

A String containing the SUB

A _SUB object evaluates to a string and the format must be a valid PNP or ACPI ID with no asterisk or other leading characters.

See the definition of _HID (_HID (Hardware ID) ) for the definition of PNP and ACPI ID strings.

Example ASL:

Name (_SUB, "MSFT3000") // Vendor-defined subsystem

6.1.10. _STR (String)¶

The _STR object evaluates to a Unicode string that describes the device or thermal zone. It may be used by an OS to provide information to an end user. This information is particularly valuable when no other information is available.

Arguments:

None

Return Value:

A Buffer containing a Unicode string that describes the device

Example ASL:

Device (XYZ) {

Name (_ADR, 0x00020001)

Name (_STR, Unicode ("ACME super DVD controller"))

}

Then, when all else fails, an OS can use the info included in the _STR object to describe the hardware to the user.

6.1.11. _SUN (Slot User Number)¶

_SUN is an object that evaluates to the slot-unique ID number for a slot. _SUN is used by OSPM UI to identify slots for the user. For example, this can be used for battery slots, PCI slots, PCMCIA slots, or swappable bay slots to inform the user of what devices are in each slot. _SUN evaluates to an integer that is the number to be used in the user interface.

Arguments:

None

Return Value:

An Integer containing the slot’s unique ID

The _SUN value is required to be unique among the slots of the same type. It is also recommended that this number match the slot number printed on the physical slot whenever possible.

6.1.12. _UID (Unique ID)¶

This object provides OSPM with a logical device ID that does not change across reboots. This object is optional, but is required when the device has no other way to report a persistent unique device ID. The _UID must be unique across all devices with either a common _HID or _CID. This is because a device needs to be uniquely identified to the OSPM, which may match on either a _HID or a _CID to identify the device. The uniqueness match must be true regardless of whether the OSPM uses the _HID or the _CID. OSPM typically uses the unique device ID to ensure that the device-specific information, such as network protocol binding information, is remembered for the device even if its relative location changes. For most integrated devices, this object contains a unique identifier.

In general, a _UID object evaluates to either a numeric value or a string. However, when defining an object with an _HID of ACPI0007 (processor definition objects), the _UID object must return an integer. This integer is used as an identifier in the MADT, PPTT and other tables to connect non-enumerable devices to a processor object. When a string is used in these cases, there is no mechanism for connecting these devices.

Arguments:

None

Return Value:

An Integer or String containing the Unique ID

6.2. Device Configuration Objects¶

This section describes objects that provide OSPM with device specific information and allow OSPM to configure device operation and resource utilization.

OSPM uses device configuration objects to configure hardware resources for devices enumerated via ACPI. Device configuration objects provide information about current and possible resource requirements, the relationship between shared resources, and methods for configuring hardware resources.

Note

these objects must only be provided for devices that cannot be configured by any other hardware standard such as PCI, PCMCIA, and soon.

When OSPM enumerates a device, it calls _PRS to determine the resource requirements of the device. It may also call _CRS to find the current resource settings for the device. Using this information, the Plug and Play system determines what resources the device should consume and sets those resources by calling the device’s _SRS control method.

In ACPI, devices can consume resources (for example, legacy keyboards), provide resources (for example, a proprietary PCI bridge), or do both. Unless otherwise specified, resources for a device are assumed to be taken from the nearest matching resource above the device in the device hierarchy.

Some resources, however, may be shared amongst several devices. To describe this, devices that share a resource (resource consumers) must use the extended resource descriptors (0x7-0xA) described in Large Resource Data Type. These descriptors point to a single device object (resource producer) that claims the shared resource in its _PRS. This allows OSPM to clearly understand the resource dependencies in the system and move all related devices together if it needs to change resources. Furthermore, it allows OSPM to allocate resources only to resource producers when devices that consume that resource appear.

The device configuration objects are listed in the table below.

Object |

Description |

|---|---|

_CCA |

Cache Coherency Attribute – specifies whether a device and its descendants support hardware managed cache coherency. |

_CDM |

Object that specifies a clock domain for a processor. |

_CRS |

Object that specifies a device’s current resource settings, or a control method that generates such an object. |

_DIS |

Control method that disables a device. |

_DMA |

Object that specifies a device’s current resources for DMA transactions. |

_DSD |

Object that evaluates to device specific information |

_FIX |

Object used to provide correlation between the fixed-hardware register blocks defined in the FADT and the devices that implement these fixed-hardware registers. |

_GSB |

Object that provides the Global System Interrupt Base for a hot-plugged I/O APIC device. |

_HMA |

Object that provides updated HMAT structures. |

_HPP |

Object that specifies the cache-line size, latency timer, SERR enable, and PERR enable values to be used when configuring a PCI device inserted into a hot-plug slot or initial configuration of a PCI device at system boot. |

_HPX |

Object that provides device parameters when configuring a PCI device inserted into a hot-plug slot or initial configuration of a PCI device at system boot. Supersedes _HPP. |

_MAT |

Object that evaluates to a buffer of Interrupt Controller Structures. |

_OSC |

An object OSPM evaluates to convey specific software support / capabilities to the platform allowing the platform to configure itself appropriately. |

_PRS |

An object that specifies a device’s possible resource settings, or a control method that generates such an object. |

_PRT |

Object that specifies the PCI interrupt routing table. |

_PXM |

Object that specifies a proximity domain for a device. |

_SLI |

Object that provides updated distance information for a system locality. |

_SRS |

Control method that sets a device’s settings. |

6.2.1. _CDM (Clock Domain)¶

This optional object conveys the processor clock domain to which a processor belongs. A processor clock domain is a unique identifier representing the hardware clock source providing the input clock for a given set of processors. This clock source drives software accessible internal counters, such as the Time Stamp Counter, in each processor. Processor counters in the same clock domain are driven by the same hardware clock source. In multi-processor platforms that utilize multiple clock domains, such counters may exhibit drift when compared against processor counters on different clock domains.

The _CDM object evaluates to an integer that identifies the device as belonging to a specific clock domain. OSPM assumes that two devices in the same clock domain are connected to the same hardware clock.

Arguments:

None

Return Value:

An Integer (DWORD) containing a clock domain identifier.

In the case the platform does not convey any clock domain information to OSPM via the SRAT or the _CDM object, OSPM assumes all logical processors to be on a common clock domain. If the platform defines _CDM object under a logical processor then it must define _CDM objects under all logical processors whose clock domain information is not provided via the SRAT.

6.2.2. _CRS (Current Resource Settings)¶

This required object evaluates to a byte stream that describes the system resources currently allocated to a device. Additionally, a bus device must supply the resources that it decodes and can assign to its children devices. If a device is disabled, then _CRS returns a valid resource template for the device, but the actual resource assignments in the return byte stream are ignored. If the device is disabled when _CRS is called, it must remain disabled.

The format of the data contained in a _CRS object follows the formats defined in Resource Data Types for ACPI, which is a compatible extension of the Plug and Play BIOS Specification (see reference below). The resource data is provided as a series of data structures, with each of the resource data structures having a unique tag or identifier. The resource descriptor data structures specify the standard PC system resources, such as memory address ranges, I/O ports, interrupts, and DMA channels.

See also

Plug and Play BIOS Specification Version 1.0A, May 5, 1994, Compaq Computer Corp., Intel Corp., Phoenix Technologies Ltd.

Arguments:

None

Return Value:

A Buffer containing a resource descriptor byte stream

6.2.3. _DIS (Disable)¶

This control method disables a device. When the device is disabled, it must not be decoding any hardware resources. Prior to running this control method, OSPM will have already put the device in the D3 state.

When a device is disabled via the _DIS, the _STA control method for this device must return with the Disabled bit set.

Arguments:

None

Return Value:

None

6.2.4. _DMA (Direct Memory Access)¶

This optional object returns a byte stream in the same format as a _CRS object. _DMA is only defined under devices that represent buses. It specifies the ranges the bus controller (bridge) decodes on the child-side of its interface. (This is analogous to the _CRS object, which describes the resources that the bus controller decodes on the parent-side of its interface.) Any ranges described in the resources of a _DMA object can be used by child devices for DMA or bus master transactions.

The _DMA object is only valid if a _CRS object is also defined. OSPM must re-evaluate the _DMA object after an _SRS object has been executed because the _DMA ranges resources may change depending on how the bridge has been configured.

If the _DMA object is not present for a bus device, the OS assumes that any address placed on a bus by a child device will be decoded either by a device on the bus or by the bus itself, (in other words, all address ranges can be used for DMA).

For example, if a platform implements a PCI bus that cannot access all of physical memory, it has a _DMA object under that PCI bus that describes the ranges of physical memory that can be accessed by devices on that bus.

A _DMA object is not meant to describe any “map register” hardware that is set up for each DMA transaction. It is meant only to describe the DMA properties of a bus that cannot be changed without reevaluating the _SRS method.

Arguments:

None

Return Value:

A Buffer containing a resource descriptor byte stream

_DMA Example ASL:

Device(BUS0)

{

//

// The _DMA method returns a resource template describing the

// addresses that are decoded on the child side of this

// bridge. The contained resource descriptors thus indicate

// the address ranges that bus masters living below this

// bridge can use to send accesses through the bridge toward a

// destination elsewhere in the system (e.g. main memory).

//

// In our case, any bus master addresses need to fall between

// 0 and 0x80000000 and will have 0x200000000 added as they

// cross the bridge. Furthermore, any child-side accesses

// falling into the range claimed in our _CRS will be

// interpreted as a peer-to-peer traffic and will not be

// forwarded upstream by the bridge.

//

// Our upstream address decoder will only claim one range from

// 0x20000000 to 0x5fffffff in the _CRS. Therefore _DMA

// should return two QWORDMemory descriptors, one describing

// the range below and one describing the range above this

// "peer-to-peer" address range.

//

Method(_DMA, ResourceTemplate()

{

QWORDMemory(

ResourceConsumer,

PosDecode, // _DEC

MinFixed, // _MIF

MaxFixed, // _MAF

Prefetchable, // _MEM

ReadWrite, // _RW

0, // _GRA

0, // _MIN

0x1fffffff, // _MAX

0x200000000, // _TRA

0x20000000, // _LEN

,

,

,

)

QWORDMemory(

ResourceConsumer,

PosDecode, // _DEC

MinFixed, // _MIF

MaxFixed, // _MAF

Prefetchable, // _MEM

ReadWrite, // _RW

0, // _GRA

0x60000000, // _MIN

0x7fffffff, // _MAX

0x200000000, // _TRA

0x20000000, // _LEN

,

,

,

)

})

}

6.2.5. _DSD (Device Specific Data)¶

This optional object is used to provide device drivers (via OSPM) with additional device properties and information. _DSD returns a variable-length package containing a list of Device Data Descriptor structures each consisting of a UUID (see Universally Unique Identifiers (UUIDs)) and a package (Data Structure). The UUID is all that is needed to define the Data Structure. The UUID itself may place a restriction based on _HID or the optional _CID, _CLS, _HRV, _SUB objects, or _HID and one of those optional objects. However, it also may not place such a restriction.

New UUIDs may be created by OEMs and IHVs or other interface or device governing bodies (e.g. the PCI SIG or the UEFI Forum), as long as the UUID is different from other published UUIDs.

The list of well-known UUIDs allocated for _DSD and the definition of data formats associated with them is available in an auxiliary document hosted on the UEFI Forum: http://www.uefi.org/acpi .

Arguments:

None

Return Value:

A variable-length Package containing a list of Device Data Descriptor structures as described below.

Return Value Information:

Package ()

{

Device Data Descriptor 0

...

Device Data Descriptor n

}

Each Device Data Descriptor structure consists of two elements, as follows:

UUID // Buffer (16 bytes)

Data Structure // Package (depending on UUID)

UUID uniquely determines the format of Data Structure.

Data Structure is a set of device specific data items the format of which is uniquely determined by the UUID and the meaning of which is uniquely determined by the UUID possibly in combination with a PNP or ACPI device ID.

Multiple Device Data Descriptor structures with the same UUID are not permitted.

_DSD must return the same data each time it is evaluated. Firmware should not expect it to be evaluated every time (in case it is implemented as a method).

Examples:

Note

The UUID used in the following examples is assumed to define the data format for Data Structure as a list of packages of length 2 (Properties) whose first element (Key) must be a String and the second element is a Value associated with that key. The set of valid Keys and the format and interpretation of the Values associated with them is then dependent on the PNP or ACPI device ID of the device.

Device (MDEV) {

Name (_HID, "PNP####")

Name (_DSD, Package () {

ToUUID("daffd814-6eba-4d8c-8a91-bc9bbf4aa301"),

Package () {

Package (2) {...}, // Property 1

...

Package (2) {...} // Property n

}

})

}

//

// PWM controller with two pins that can be driven and a device using

// those pins with the periods of 5000000 and 4500000 nanoseconds,

// respectively.

//

Device (\_SB.PCI0.PWM) {

Name (_HID, "PNP####")

Name (_DSD, Package () {

ToUUID("daffd814-6eba-4d8c-8a91-bc9bbf4aa301"),

Package () {

Package (2) {"#pwm-cells", 2}

}

})

}

Device (\_SB.PCI0.BL) {

Name (_HID, "ACPI####")

Name (_DSD, Package () {

ToUUID("daffd814-6eba-4d8c-8a91-bc9bbf4aa301"),

Package () {

Package (2) {

"pwms",

Package () {

\_SB.PCI0.PWM, 0, 5000000,

\_SB.PCI0.PWM, 1, 4500000

}

}

}

})

}

//

// SPI controller using a fixed frequency clock represented by the CLKO

// device object.

//

Device (\_SB_.PCI0) {

Device (CLK0) {

Name (_HID, "PNP####")

Name (_DSD, Package () {

ToUUID("daffd814-6eba-4d8c-8a91-bc9bbf4aa301"),

Package () {

Package (2) {"#clock-cells", 0},

Package (2) {"clock-frequency", 120000000}

}

})

}

Device (SPI0) {

Name (_HID, "PNP####")

Name (_DSD, Package () {

ToUUID("daffd814-6eba-4d8c-8a91-bc9bbf4aa301"),

Package () {

Package (2) {"clocks", Package () {1, ^CLK0}}

}

})

...

}

}

6.2.6. _FIX (Fixed Register Resource Provider)¶

This optional object is used to provide a correlation between the fixed-hardware register blocks defined in the FADT and the devices in the ACPI namespace that implement these fixed-hardware registers. This object evaluates to a package of Plug and Play-compatible IDs (32-bit compressed EISA type IDs) that correlate to the fixed-hardware register blocks defined in the FADT. The device under which _FIX appears plays a role in the implementation of the fixed-hardware (for example, implements the hardware or decodes the hardware’s address). _FIX conveys to OSPM whether a given device can be disabled, powered off, or should be treated specially by conveying its role in the implementation of the ACPI fixed-hardware register interfaces. This object takes no arguments.

The _CRS object describes a device’s resources. That _CRS object may contain a superset of the resources in the FADT, as the device may actually decode resources beyond what the FADT requires. Furthermore, in a machine that performs translation of resources within I/O bridges, the processor-relative resources in the FADT may not be the same as the bus-relative resources in the _CRS.

Arguments:

None

Return Value:

A variable-length Package containing a list of Integers, each containing a PNP ID

Each of fields in the FADT has its own corresponding Plug and Play ID, as shown below:

PNP0C20 - SMI_CMD

PNP0C21 - PM1a_EVT_BLK / X\_ PM1a_EVT_BLK

PNP0C22 - PM1b_EVT_BLK / X_PM1b_EVT_BLK

PNP0C23 - PM1a_CNT_BLK / X_PM1a_CNT_BLK

PNP0C24 - PM1b_CNT_BLK / X\_ PM1b_CNT_BLK

PNP0C25 - PM2_CNT_BLK / X\_ PM2_CNT_BLK

PNP0C26 - PM_TMR_BLK / X\_ PM_TMR_BLK

PNP0C27 - GPE0_BLK / X_GPE0_BLK

PNP0C28 - GPE1_BLK / X\_ GPE1_BLK

PNP0B00 - FIXED_RTC

PNP0B01 - FIXED_RTC

PNP0B02 - FIXED_RTC

Example ASL for _FIX usage:

Scope(\_SB) {

Device(PCI0) { // Root PCI Bus

Name(_HID, EISAID("PNP0A03")) // Need \_HID for root device

Method (_CRS,0){ // Need current resources for root device

// Return current resources for root bridge 0

}

Name(_PRT, Package(){ // Need PCI IRQ routing for PCI bridge

// Package with PCI IRQ routing table information

})

Name(_FIX, Package(1) {

EISAID("PNP0C25")} // PM2 control ID

)

Device (PX40) { // ISA

Name(_ADR,0x00070000)

Name(_FIX, Package(1) {

EISAID("PNP0C20")} // SMI command port

)

Device (NS17) { // NS17 (Nat. Semi 317, an ACPI part)

Name(_HID, EISAID("PNP0C02"))

Name(_FIX, Package(3) {

EISAID("PNP0C22"), // PM1b event ID

EISAID("PNP0C24"), // PM1b control ID

EISAID("PNP0C28")} // GPE1 ID

}

} // end PX40

Device (PX43) { // PM Control

Name(_ADR,0x00070003)

Name(_FIX, Package(4) {

EISAID("PNP0C21"), // PM1a event ID

EISAID("PNP0C23"), // PM1a control ID

EISAID("PNP0C26"), // PM Timer ID

EISAID("PNP0C27")} // GPE0 ID

)

} // end PX43

} // end PCI0

} // end scope SB

6.2.7. _GSB (Global System Interrupt Base)¶

_GSB is an optional object that evaluates to an integer that corresponds to the Global System Interrupt Base for the corresponding I/O APIC device. The I/O APIC device may either be bus enumerated (e.g. as a PCI device) or enumerated in the namespace as described in I/O APIC Device. Any I/O APIC device that either supports hot-plug or is not described in the MADT must contain a _GSB object.

If the I/O APIC device also contains a _MAT object, OSPM evaluates the _GSB object first before evaluating the _MAT object. By providing the Global System Interrupt Base of the I/O APIC, this object enables OSPM to process only the _MAT entries that correspond to the I/O APIC device. See _MAT (Multiple APIC Table Entry). Since _MAT is allowed to potentially return all the MADT entries for the entire platform, _GSB is needed in the I/O APIC device scope to enable OSPM to identify the entries that correspond to that device.

If an I/O APIC device is activated by a device-specific driver, the physical address used to access the I/O APIC will be exposed by the driver and cannot be determined from the _MAT object. In this case, OSPM cannot use the _MAT object to determine the Global System Interrupt Base corresponding to the I/O APIC device and hence requires the _GSB object.

The Global System Interrupt Base is a 64-bit value representing the corresponding I/OAPIC device as defined in Global System Interrupts.

Arguments:

None Return Value: An Integer containing the interrupt base

Example ASL for _GSB usage for a non-PCI based I/O APIC Device:

Scope(\_SB) {

...

Device(APIC) { // I/O APIC Device

Name(_HID, "ACPI0009") // ACPI ID for I/O APIC

Name(_CRS, ResourceTemplate()

{ ...}) // only one resource pointing to I/O APIC register base

Method(_GSB){

Return (0x10) // Global System Interrupt Base for I/O APIC starts at 16

}

} // end APIC

} // end scope SB

Example ASL for _GSB usage for a PCI-based I/O APIC Device:

Scope(\_SB) {

Device(PCI0) // Host bridge

Name(_HID, EISAID("PNP0A03")) // Need \_HID for root device

Device(PCI1) { // I/O APIC PCI Device

Name(_ADR,0x00070000)

Method(_GSB){

Return (0x18) // Global System Interrupt Base for I/O APIC starts at 24

}

} // end PCI1

} // end PCI0

} // end scope SB

6.2.8. _HPP (Hot Plug Parameters)¶

This optional object evaluates to a package containing the cache-line size, latency timer, SERR enable, and PERR enable values to be used when configuring a PCI device inserted into a hot-plug slot or for performing configuration of a PCI devices not configured by the platform boot firmware at system boot. The object is placed under a PCI bus where this behavior is desired, such as a bus with hot-plug slots. _HPP provided settings apply to all child buses, until another _HPP object is encountered.

Arguments:

None

Return Value:

A Package containing the Integer hot-plug parameters

Example:

Method (_HPP, 0) {

Return (Package(4){

0x08, // CacheLineSize in DWORDS

0x40, // LatencyTimer in PCI clocks

0x01, // Enable SERR (Boolean)

0x00 // Enable PERR (Boolean)

})

}

Field |

Object Type |

Definition |

|---|---|---|

Cache-line size |

Integer |

Cache-line size reported in number of DWORDs. |

Latency timer |

Integer |

Latency timer value reported in number of PCI clock cycles. |

Enable SERR |

Integer |

When set to 1, indicates that action must be performed to enable SERR in the command register. |

Enable PERR |

Integer |

When set to 1, indicates that action must be performed to enable PERR in the command register. |

Example: Using _HPP

Scope(\_SB) {

Device(PCI0) { // Root PCI Bus

Name(_HID, EISAID("PNP0A03")) // \_HID for root device

Method (_CRS,0){ // Need current resources for root dev

// Return current resources for root bridge 0

}

Name(_PRT, Package(){ // Need PCI IRQ routing for PCI bridge

// Package with PCI IRQ routing table information

})

Device (P2P1) { // First PCI-to-PCI bridge (No Hot Plug slots)

Name(_ADR,0x000C0000) // Device#Ch, Func#0 on bus PCI0

Name(_PRT, Package(){ // Need PCI IRQ routing for PCI bridge

// Package with PCI IRQ routing table information

})

} // end P2P1

Device (P2P2) {

// Second PCI-to-PCI bridge (Bus contains Hot plug slots)

Name(_ADR,0x000E0000) // Device#Eh, Func#0 on bus PCI0

Name(_PRT, Package(){ // Need PCI IRQ routing for PCI bridge

// Package with PCI IRQ routing table information

})

Name(_HPP, Package(){0x08,0x40, 0x01, 0x00})

// Device definitions for Slot 1- HOT PLUG SLOT

Device (S1F0) { // Slot 1, Func#0 on bus P2P2

Name(_ADR,0x00020000)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S1F1) { // Slot 1, Func#1 on bus P2P2

Name(_ADR,0x00020001)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S1F2) { // Slot 1, Func#2 on bus P2P2

Name(_ADR,0x000200 02)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S1F3) { // Slot 1, Func#3 on bus P2P2

Name(_ADR,0x00020003)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S1F4) { // Slot 1, Func#4 on bus P2P2

Name(_ADR,0x00020004)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S1F5) { // Slot 1, Func#5 on bus P2P2

Name(_ADR,0x00020005)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S1F6) { // Slot 1, Func#6 on bus P2P2

Name(_ADR,0x00020006)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S1F7) { // Slot 1, Func#7 on bus P2P2

Name(_ADR,0x00020007)

Method(_EJ0, 1) { // Remove all power to device}

}

// Device definitions for Slot 2- HOT PLUG SLOT

Device (S2F0) { // Slot 2, Func#0 on bus P2P2

Name(_ADR,0x00030000)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S2F1) { // Slot 2, Func#1 on bus P2P2

Name(_ADR,0x00030001)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S2F2) { // Slot 2, Func#2 on bus P2P2

Name(_ADR,0x00030002)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S2F3) { // Slot 2, Func#3 on bus P2P2

Name(_ADR,0x00030003)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S2F4) { // Slot 2, Func#4 on bus P2P2

Name(_ADR,0x00030004)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S2F5) { // Slot 2, Func#5 on bus P2P2

Name(_ADR,0x00030005)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S2F6) { // Slot 2, Func#6 on bus P2P2

Name(_ADR,0x00030006)

Method(_EJ0, 1) { // Remove all power to device}

}

Device (S2F7) { // Slot 2, Func#7 on bus P2P2

Name(_ADR,0x00030007)

Method(_EJ0, 1) { // Remove all power to device}

}

} // end P2P2

} // end PCI0

} // end Scope (\_SB)

OSPM will configure a PCI device on a card hot-plugged into slot 1 or slot 2, with a cache line size of 32 (Notice this field is in DWORDs), latency timer of 64, enable SERR, but leave PERR alone.

6.2.9. _HPX (Hot Plug Parameter Extensions)¶

This optional object provides platform-specific information to the OSPM PCI driver component responsible for configuring PCI, PCI-X, or PCI Express Functions. The information conveyed applies to the entire hierarchy downward from the scope containing the _HPX object. If another _HPX object is encountered downstream, the settings conveyed by the lower-level object apply to that scope downward.

OSPM uses the information returned by _HPX to determine how to configure PCI Functions that are hot-plugged into the system, to configure Functions not configured by the platform firmware during initial system boot, and to configure Functions any time they lose configuration space settings (e.g. OSPM issues a Secondary Bus Reset/Function Level Reset or Downstream Port Containment is triggered). The _HPX object is placed within the scope of a PCI-compatible bus where this behavior is desired, such as a bus with hot-plug slots. It returns a single package that contains one or more sub-packages, each containing a single Setting Record. Each such Setting Record contains a Setting Type (INTEGER), a Revision number (INTEGER) and type/revision specific contents.

The format of data returned by the _HPX object is extensible. The Setting Type and Revision number determine the format of the Setting Record. OSPM ignores Setting Records of types that it does not understand. A Setting Record with higher Revision number supersedes that with lower revision number, however, the _HPX method can return both together, OSPM shall use the one with highest revision number that it understands. Type 3 records may have multiple records with the same revision or different revision (refer to the Revision field in PCI Express Descriptor Setting Record Content. Out of all the Type 3 records, the OSPM shall determine the highest revision number that it understands and use all Type 3 records with that revision.

_HPX may return multiple types or Record Settings (each setting in a single sub-package.) OSPM is responsible for detecting the type of Function and for applying the appropriate settings. OSPM is also responsible for detecting the device / port type of the PCI Express Function and applying the appropriate settings provided. For example, the Secondary Uncorrectable Error Severity and Secondary Uncorrectable Error Mask settings of Type 2 record are only applicable to PCI Express to PCI-X/PCI Bridge whose device / port type is 1000b. Similarly, AER settings are only applicable to hot plug PCI Express devices that support the optional AER capability.

Arguments:

None

Return Value:

A variable-length Package containing a list of Packages, each containing a single PCI, PCI-X, PCI Express, or PCI Express Descriptor Record Setting as described below

The _HPX object supersedes the _HPP object. If the _HPP and _HPX objects exist within a device’s scope, OSPM will only evaluate the _HPX object.

Note

OSPM may override the settings provided by the _HPX object’s Type2 record (PCI Express Settings) or Type3 record (PCI Express Descriptor Settings) when OSPM has assumed native control of the corresponding feature. For example, if OSPM has assumed ownership of AER (via _OSC), OSPM may override AER related settings returned by _HPX.

Note

Since error status registers do not drive error signaling, OSPM is not required to clear error status registers as part of _HPX handling.

Note

There are other mechanisms besides _HPX that provide platform-specific information to the OSPM PCI driver component responsible for configuring PCI, PCI-X, or PCI Express Functions (e.g., _DSM Definitions for Latency Tolerance Reporting as defined in the PCI Firmware Specification). System firmware should only provide platform-specific information via one of these mechanisms for any given register or feature (i.e., if Latency Tolerance Reporting information is provided via _DSM Definitions for Latency Tolerance Reporting then no information related to Latency Tolerance Reporting should be provided by _HPX and vice versa). Failure to do so will result in undefined behavior from the OSPM.

6.2.9.1. PCI Setting Record (Type 0)¶

The PCI setting record contains the setting type 0, the current revision 1 and the type/revision specific content: cache-line size, latency timer, SERR enable, and PERR enable values.

Field |

Object Type |

Definition |

|---|---|---|

Header |

||

- Type |

Integer |

0x00: Type 0 (PCI) setting record. |

- Revision |

Integer |

0x01: Revision 1, defining the set of fields below. |

Cache-line size |

Integer |

Cache-line size reported in number of DWORDs. |

Latency timer |

Integer |

Latency timer value reported in number of PCI clock cycles. |

Enable SERR |

Integer |

When set to 1, indicates that action must be performed to enable SERR in the command register. |

Enable PERR |

Integer |

When set to 1, indicates that action must be performed to enable PERR in the command register. |

If the hot plug device includes bridge(s) in the hierarchy, the above settings apply to the primary side (command register) of the hot plugged bridge(s). The settings for the secondary side of the bridge(s) (Bridge Control Register) are assumed to be provided by the bridge driver.

The Type 0 record is applicable to hot plugged PCI, PCI-X and PCI Express devices. OSPM will ignore settings provided in the Type0 record that are not applicable (for example, Cache-line size and Latency Timer are not applicable to PCI Express).

6.2.9.2. PCI-X Setting Record (Type 1)¶

The PCI-X setting record contains the setting type 1, the current revision 1 and the type/revision specific content: the maximum memory read byte count setting, the average maximum outstanding split transactions setting and the total maximum outstanding split transactions to be used when configuring PCI-X command registers for PCI-X buses and/or devices.

Field |

Object Type |

Definition |

|---|---|---|

Header |

||

- Type |

Integer |

0x01: Type 1 (PCI-X) setting record. |

- Revision |

Integer |

0x01: Revision 1, defining the set of fields below. |

Maximum memory read byte count |

Integer |

Maximum memory read byte count reported: Value 0: Maximum byte count 512 Value 1: Maximum byte count 1024 Value 2: Maximum byte count 2048 Value 3: Maximum byte count 4096 |

Average maximum outstanding split transactions |

Integer |

The following values are defined: Value 0: Maximum outstanding split transaction 1 Value 1: Maximum outstanding split transaction 2 Value 2: Maximum outstanding split transaction 3 Value 3: Maximum outstanding split transaction 4 Value 4: Maximum outstanding split transaction 8 Value 5: Maximum outstanding split transaction 12 Value 6: Maximum outstanding split transaction 16 Value 7: Maximum outstanding split transaction 32 |

Total maximum outstanding split transactions |

Integer |

See the definition for the average maximum outstanding split transactions. |

For simplicity, OSPM could use the Average Maximum Outstanding Split Transactions value as the Maximum Outstanding Split Transactions register value in the PCI-X command register for each PCI-X device. Another alternative is to use a more sophisticated policy and the Total Maximum Outstanding Split Transactions Value to gain even more performance. In this case, the OS would examined each PCI-X device that is directly attached to the host bridge, determine the number of outstanding split transactions supported by each device, and configure each device accordingly. The goal is to ensure that the aggregate number of concurrent outstanding split transactions does not exceed the Total Maximum Outstanding Split Transactions Value: an integer denoting the number of concurrent outstanding split transactions the host bridge can support (the minimum value is 1).

This object does not address providing additional information that would be used to configure registers in bridge devices, whether architecturally-defined or specification-defined registers or device specific registers. It is expected that a driver for a bridge would be the proper implementation mechanism to address both of those issues. However, such a bridge driver should have access to the data returned by the _HPX object for use in optimizing its decisions on how to configure the bridge. Configuration of a bridge is dependent on both system specific information such as that provided by the _HPX object, as well as bridge specific information.

6.2.9.3. PCI Express Setting Record (Type 2)¶

The PCI Express setting record contains the setting type 2, the current revision 1 and the type/revision specific content (the control registers as listed in the table below) to be used when configuring registers in the Advanced Error Reporting Extended Capability Structure or PCI Express Capability Structure for the PCI Express devices.

The Type 2 Setting Record allows a PCI Express-aware OS that supports native hot plug to configure the specified registers of the hot plugged PCI Express device. A PCI Express-aware OS that has assumed ownership of native hot plug (via _OSC) but does not support or does not have ownership of the AER register set must use the data values returned by the _HPX object’s Type 2 record to program the AER registers of a hot-added PCI Express device. However, since the Type 2 record also includes register bits that have functions other than AER, OSPM must ignore values contained within this setting record that are not applicable.

To support PCIe RsvdP semantics for reserved bits, two values for each register are provided: an “AND mask” and an “OR mask”. Each bit understood by firmware to be RsvdP shall be set to 1 in the “AND mask” and 0 in the “OR mask”. Each bit that firmware intends to be configured as 0 shall be set to 0 in both the “AND mask” and the “OR mask”. Each bit that firmware intends to be configured a 1 shall be set to 1 in both the “AND mask” and the “OR mask”.

When configuring a given register, OSPM uses the following algorithm:

Read the register’s current value, which contains the register’s default value.

Perform a bit-wise AND operation with the “AND mask” from the table below.

Perform a bit-wise OR operation with the “OR mask” from the table below.

Override the computed settings for any bits if deemed necessary. For example, if OSPM is aware of an architected meaning for a bit that firmware considers to be RsvdP, OSPM may choose to override the computed setting for that bit. Note that firmware sets the “AND value” to 1 and the “OR value” to 0 for each bit that it considers to be RsvdP.

Write the end result value back to the register.

Note that the size of each field in the following table matches the size of the corresponding PCI Express register.

Field |

Object Type |

Definition |

|---|---|---|

Header |

||

- Type |

Integer |

0x02: Type 2 (PCI Express) setting record. |

- Revision |

Integer |

0x01: Revision 1, defining the set of fields below. |

Uncorrectable Error Mask Register AND Mask |

Integer |

Bits [31:0] contain the “AND mask” to be used in the OSPM algorithm described above. |

Uncorrectable Error Mask Register OR Mask |

Integer |

Bits [31:0] contain the “OR mask” to be used in the OSPM algorithm described above. |

Uncorrectable Error Severity Register AND Mask |

Integer |

Bits [31:0] contain the “AND mask” to be used in the OSPM algorithm described above. |

Uncorrectable Error Severity Register OR Mask |

Integer |

Bits [31:0] contain the “OR mask” to be used in the OSPM algorithm described above. |

Correctable Error Mask Register AND Mask |

Integer |

Bits [31:0] contain the “AND mask” to be used in the OSPM algorithm described above. |

Correctable Error Mask Register OR Mask |

Integer |

Bits [31:0] contain the “OR mask” to be used in the OSPM algorithm described above. |

Advanced Error Capabilities and Control Register AND Mask |

Integer |

Bits [31:0] contain the “AND mask” to be used in the OSPM algorithm described above. |

Advanced Error Capabilities and Control Register OR Mask |

Integer |

Bits [31:0] contain the “OR mask” to be used in the OSPM algorithm described above. |

Device Control Register AND Mask |

Integer |

Bits [15 :0] contain the “AND mask” to be used in the OSPM algorithm described above. |

Device Control Register OR Mask |

Integer |

Bits [15:0] contain the “OR mask” to be used in the OSPM algorithm described above. |

Link Control Register AND Mask |

Integer |

Bits [15 :0] contain the “AND mask” to be used in the OSPM algorithm described above. |

Link Control Register OR Mask |

Integer |

Bits [15 :0] contain the “OR mask” to be used in the OSPM algorithm described above. |

Secondary Uncorrectable Error Severity Register AND Mask |

Integer |

Bits [31 :0] contain the “AND mask” to be used in the OSPM algorithm described above |

Secondary Uncorrectable Error Severity Register OR Mask |

Integer |

Bits [31 :0] contain the “OR mask” to be used in the OSPM algorithm described above |

Secondary Uncorrectable Error Mask Register AND Mask |

Integer |

Bits [31 :0] contain the “AND mask” to be used in the OSPM algorithm described above |

Secondary Uncorrectable Error Mask Register OR Mask |

Integer |

Bits [31 :0] contain the “OR mask” to be used in the OSPM algorithm described above |

6.2.9.4. PCI Express Descriptor Setting Record (Type 3)¶

The PCI Express Descriptor setting record contains the setting type 3, the current revision 1 and the type/revision specific content (the control registers as listed in the tables below) to be used when configuring registers in PCI Express Functions. There may be multiple PCI Express Descriptor setting records in a single _HPX object with the same or different revision. Each PCI Express Descriptor setting record shall contain at least one, and may contain more than one, PCI Express Register Descriptors as defined in PCI Express Register Descriptor.

The Type 3 Setting Record allows a PCI Express-aware OS to configure the indicated registers of the PCI Express Function. A PCI Express-aware OS that does not support or does not have ownership of a register in this record must use the data values returned by the _HPX object’s Type 3 record to program that register of a PCI Express Function that has lost its configuration space settings (e.g. a hot-added device, a device not configured by the platform firmware during initial system boot, a Device/Function that was reset via Secondary Bus Reset/Function Level Reset, Downstream Port Containment was triggered, etc.).

To support PCIe RsvdP semantics for reserved bits, two values for each register indicated by Write Register Offset are provided: a Write AND Mask and a Write OR Mask. Each bit understood by firmware to be RsvdP shall be set to 1 in the Write AND Mask and 0 in the Write OR Mask. Each bit that firmware intends to be configured as 0 shall be set to 0 in both the Write AND Mask and the Write OR Mask. Each bit that firmware intends to be configured a 1 shall be set to 1 in both the Write AND Mask and the Write OR Mask.

OSPM evaluates each PCI Express Register Descriptor in order starting with the first PCI Express Register Descriptor and continuing through the Nth PCI Express Register Descriptor as shown in PCI Express Descriptor Setting Record Content for each PCI Express Function that has lost its configuration space settings (e.g. a hot-added device, a device not configured by the platform firmware during initial system boot, a Device/Function that was reset via Secondary Bus Reset/Function Level Reset, Downstream Port Containment was triggered, etc.) in the scope of the _HPX method using the following algorithm:

Verify the PCI Express Register Descriptor applies to the PCI Express Function.

Read the PCI Express Function’s Device Type/Port from its PCI Express Capabilities Register.

Read the bit corresponding to the PCI Express Function’s Device Port/Type in the Device/Port Type from PCI Express Register Descriptor below.

If set to 0b, then the PCI Express Register Descriptor does not apply to the PCI Express Function and OSPM moves to the next Function in the scope of the _HPX method or the next PCI Express Register Descriptor if there are no more Functions.

If set to 1b, then continue to the next step.

Determine if the PCI Express Function is a non-SR-IOV Function, an SR-IOV Physical Function, or an SR-IOV Virtual Function.

Read the bit corresponding to the PCI Express Function’s type in the Function Type from PCI Express Register Descriptor below.

If set to 0b, then the PCI Express Register Descriptor does not apply to the PCI Express Function and OSPM moves to the next Function in the scope of the _HPX method or to the next PCI Express Register Descriptor if there are no more Functions.

If set to 1b, then the PCI Express Register Descriptor applies to the PCI Express Function and OSPM continues to the next step.

Read the Configuration Space Location from PCI Express Register Descriptor below.

If Configuration Space Location is 0, then the Match Register Offset and Write Register Offset field’s byte offset is relative to offset 0 of the Function’s configuration space.

If Configuration Space Location is 1, then the Match Register Offset and Write Register Offset field’s byte offset is relative to the starting offset of the Capability Structure indicated by PCIe Capability ID.

If the Capability ID is 01h (PCI Power Management Capability Structure) or 10h (PCI Express Capability Structure) then OSPM shall check the Capability Version of the Function’s Capability Structure against the PCIe Capability ID field. In the event that there are more than one PCI Express Register Descriptors for a given PCIe Capability ID with different PCIe Capability Versions, OSPM shall use the PCI Express Register Descriptors with the highest PCIe Capability Version supported by the Function.

There may be more than one instance of a Capability Structure that matches the indicated PCIe Capability ID. Continue to step 3 for each such instance. If no Capability Structures indicated by PCIe Capability ID are found, then start back at step 1 above for the next Function in the scope of the _HPX method or the next PCI Express Register Descriptor if there are no more Functions.

If Configuration Space Location is 2, then the Match Register Offset and Write Register Offset field’s byte offset is relative to the starting offset of the Extended Capability Structure indicated by PCIe Capability ID and PCIe Capability Version.

In the event that there are more than one PCI Express Register Descriptors for a given PCIe Capability ID with different PCIe Capability Versions, OSPM shall use the PCI Express Register Descriptors with the highest PCIe Capability Version supported by the Function.

There may be more than one instance of an Extended Capability Structure that matches the indicated PCIe Capability ID and PCIe Capability Version. Continue to step 3 for each such instance. If no Extended Capability Structures indicated by PCIe Capability ID and PCIe Capability Version are found, then start back at step 1 above for the next Function in the scope of the _HPX method or the next PCI Express Register Descriptor if there are no more Functions.

If Configuration Space Location is 3, then the Match Register Offset and Write Register Offset field’s byte offset is relative to the starting offset of the Extended Capability Structure indicated by PCIe Capability ID, PCIe Capability Version, PCIe Vendor ID, VSEC ID, and VSEC Rev.

In the event that there are more than one PCI Express Register Descriptors for a given PCIe Capability ID with different PCIe Capability Versions, OSPM shall use the PCI Express Register Descriptors with the highest PCIe Capability Version supported by the Function.

Once the PCI Express Register Descriptors that match the PCIe Capability ID with the highest PCIe Capability Version supported by the Function are found, the OSPM shall use PCI Express Register Descriptors among those with the highest VSEC Rev supported by the Function.