14. Super I/O and ISA Host Controller Interactions¶

14.1. Design Descriptions¶

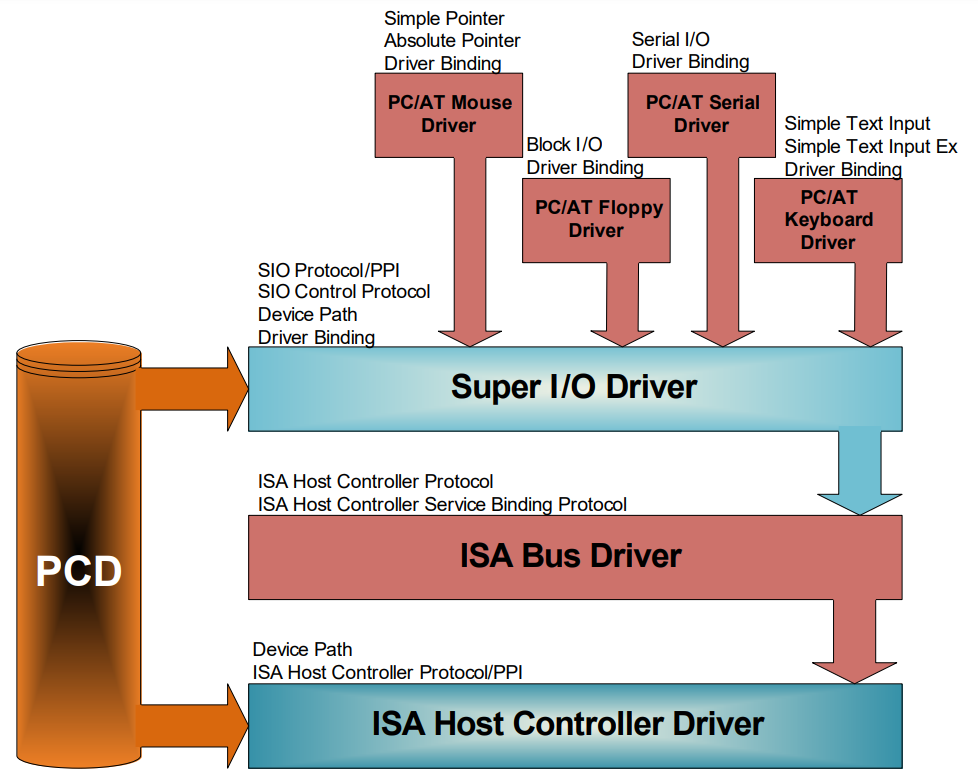

The PI architecture provides a means to interact in a standard fashion with Super I/O devices. For the purposes of this specification, the Super I/O is a device residing on an ISA or LPC or similar bus that consumes I/O and/or memory resources and provides multiple standard logical devices, such as PC/AT compatible floppy, serial port, parallel port, keyboard or mouse. There may be more than one of these devices behind each of the ISA/LPC buses.

Fig. 14.1 Super I/O and ISA Host Controller Interactions¶

Mouse, Floppy, Serial and keyboard Drivers

The Mouse, Floppy, Serial and Keyboard drivers are UEFI driver-model drivers that support devices produced by the Super I/O component. When started, they use the optional SIO Control protocol to enable the logical device, to produce the standard UEFI protocols used for console or booting, such as Serial I/O or Block I/O. They typically examine the device paths on the child handles created by the Super I/O drivers for the ACPI device path nodes that refer to their devices (e.g. PNP0501, PNP0303, etc.).

Super I/O Driver

The Super I/O driver consists of a UEFI driver-model driver (in DXE) and PEIM (in PEI) that supports a Super I/O component. The Super I/O components support multiple logical devices, such as the PS/2 keyboard controller, a floppy controller or serial/IrDa controller. When started, the Super I/O driver verifies it is present on the board and produces child handles for each of the logical devices that are enabled. On each child handle it installs an instance of the Device Path protocol, the SIO protocol and the SIO Control protocol.

ISA Bus Driver

The ISA Bus driver consists of a UEFI driver-model driver (DXE only) that produces the ISA Host Controller Service Binding protocol, which manages the many-to-one relationship between Super I/O drivers in the system and an ISA Host Controller.

ISA Host Controller Driver

The ISA Host Controller driver is a DXE driver that supports a PCI-ISA or PCI-LPC bridge component. It creates a child handle that represents the ISA Bus and installs the ISA Host Controller protocol and the Device Path protocol with an ACPI device path node (PNP0A05/PNP0A06).

PCD

The Platform Configuration Database (PCD) provides configuration information about the device configuration. Information concerning configured I/O addresses can be placed into the PCD by platform drivers and then used by the various silicon drivers, including SIO to find base addresses and logical device configuration.

14.1.1. Super I/O¶

The Super I/O DXE driver and PEIM encapsulate the functionality of the Super I/O component. They are both responsible to:

Detect the presence of the component, using information from the PCD and the apertures opened by the ISA host controller.

Configure the component and its logical devices using information from the PCD.

Publish information about the component and the logical devices it supports using the SIO protocol/PPI.

14.1.1.1. DXE¶

The Super I/O DXE Driver is responsible for: - Producing the Driver Binding protocol’s Supported() , Start() and Stop() member functions on the driver image handle. - Installing the same GUID as used for the SioGuid member of the Super I/O PPI on the image handle. This allows other drivers to detect which Super I/O is present in the system. - Checking Super I/O controller presence. The Supported() function must check whether the Super I/O controller is present in the system and whether the handle has an instance of the ISA Host Controller Service Binding protocol installed on it. For more information, see “Working With The ISA Bus”, below. - Creatingchild handles for each logical device. The Start() function creates a child handle for each logical device using the ISA Host Controller Service Binding protocol and installs the SIO and SIO Control protocols on each one. For more information, see “Working With Logical Devices”, below.

14.1.1.1.1. Working with the ISA Bus¶

The system may contain an ISA bus bridge and zero or more Extended I/O bus bridges. The Super I/O driver checks each of these to see whether it is present.

Supported()

The Super I/O DXE driver’s Driver Binding protocol Supported() function typically performs the following steps:

Verifies that the controller handle has an installed instance of the ISA Host Controller Service Binding protocol.

Opens the apertures necessary to access the component’s configuration I/O address (i.e. 0x2e/0x2f) using the ISA Host Controller protocol.

Verifies the device’s signature to determine whether the component is actually present using these configuration I/O addresses. For example, it might read a device-specific register and check for a signature.

Closes the aperture and any opened protocols.

Start()

The Super I/O DXE driver’s Driver Binding protocol Start() function typically performs the following steps:

Detects whether Super I/O DXE driver is already managing the device indicated by the configuration I/O address. One method of doing this is to create a Device Path with the configuration I/O address embedded in one device node, then use LocateDevicePath to determine whether a child handle with the ISA Host Controller protocol installed, exists.

Creates a child handle for the SIO using the ISA Host Controller Service Binding protocol.

Opens the I/O apertures used for the configuration I/O address.

Installs an instance of the Device Path and (optionally) the SIO and SIO Control protocol

Creates child handles for each logical device. Install an instance of the Device Path and SIO protocol and (optionally) the SIO Control protocol on each child handle.

Installs an instance of the Device Path, SIO and SIO Control protocols on each of the child handles.

Stop()

The Super I/O DXE driver’s Driver Binding protocol Stop() function typically performs the following steps:

Uninstalls the instances of the Device Path, SIO and SIO control protocols from each of the child handles.

Destroys the Super I/O’s own child handle using the ISA Host Controller Service Binding protocol.

SetResources()

The Super I/O DXE driver’s SIO protocol SetResources() function typically calls the OpenIoAperture() and CloseIoAperture() member functions of the ISA Host Controller protocol for the I/O addresses related to the individual logical devices.

14.1.1.1.2. Working with Logical Devices¶

The Super I/O controller supports many different logical devices. Some of these devices, such as the floppy controller, keyboard controller, MIDI controller and serial port are standard PC/AT devices. These drivers produce interfaces based on these industry-standard interfaces. Also, the Super I/O component itself may act as a logical device.

For each logical device, the following steps are taken during Start() :

Create a child handle.

Install the EFI_SIO_PROTOCOL (with correct current resource settings) on the child handle.

Install the EFI_SIO_CONTROL_PROTOCOL on the same child handle. This protocol allows a standard drivers to correctly enable and disable their resources when the Start() and Stop() members of the Driver Binding protocol that they produce is called.

If the device implements one of the standard PC/AT devices, install the EFI_DEVICE_PATH_PROTOCOL by appending a device node containing the ACPI HID of the PC/AT device to the device path of the ISA bus on which it is installed.

For more information, see “Logical Devices”

14.1.1.2. PEI¶

The Super I/O PEIM is responsible to:

Read its configuration information from the PCD.

Detect if the Super I/O device is present in the system. If necessary, it should open the aperture required to access the configuration registers using the ISA Host Controller PPI. If the Super I/O device is not detected, the driver should close the aperture and exit immediately.

Install the EFI_SIO_PPI for the Super I/O. The Identifier field allows consumers of the PPI to know which device’s register set can be accessed by using the PPI’s functions, in cases where multiple Super I/Os are supported on a platform.

Allocate I/O and memory resources. All I/O and memory resources are allocated using the EFI_ISA_HC_PPI , which handles opening and closing bridge apertures.

The Super I/O PEIM should have the EFI_ISA_HC_PPI in its dependency expression.

14.1.2. ISA Bus¶

The ISA Bus is the logical device that manages the child devices attached to the ISA Host Controller.

It consumes the ISA Host Controller protocol produced by the ISA Host Controller and installs the ISA Host Controller Service Binding protocol on the ISA Host Controller’s handle.

14.1.3. ISA Host Controller¶

The Host Controller is the device that translates the memory and I/O cycles from a parent device (such as a PCI bus) into memory and I/O cycles for the target devices.

14.1.3.1. DXE¶

The ISA Host Controller driver creates a child handle for the ISA Host Controller and installs an instance of the ISA Host Controller protocol and Device Path protocol on it. The Device Path instance for the child handle will have an extra ACPI device path node for either PNP0A05 (standard subtractive-decode ISA bus) or PNP0A06 (positive-decode extended I/O bus). If a bridge device can support more than one of these simultaneously, the _UID field of the device path node must contain a different value.

For PCI-ISA/LPC bridges, there are two classes of the ISA Host Controller Driver: generic and chipset-specific. The generic ISA Bus driver connects to any standard subtractive-decode PCI-ISA bridge device (class code:6, sub-class: 1, programming I/F 0).

Chipset-specific ISA Bus Drivers are used for PCI-ISA (or PCI-LPC) bridges that support positive decode. These bridges have device-specific mechanisms for opening and closing the I/O and memory apertures. These apertures determine which address ranges will be passed through to devices attached to the ISA/LPC side of the bridge. In this case, the registration process includes opening of apertures and guaranteeing that I/O access falls within the addresses that go the specified bus.

The ISA Host Controller is responsible for reporting the actual address and size of the apertures using the DXE GCD services.

14.1.3.2. PEI¶

The ISA Bus PEIM comes in two versions: generic and chipset-specific.

The generic version is used for subtractive-decode ISA (or LPC) buses. It implements the EFI_ISA_HC_PPI with a device identifier of all zeroes. All of the aperture functions report EFI_UNSUPPORTED .

The chipset-specific version implements the EFI_ISA_HC_PPI , which opens and close apertures for ISA/LPC buses that are positive decode. The device identifier is filled in with the PCI PFA of the PCI-ISA bridge device.

14.1.4. Logical Devices¶

Logical Device drivers are UEFI driver model drivers that support many of the standard PC/AT peripherals. They are designed to connect to the device paths produced by the Super I/O DXE driver. Each of these drivers produces the Driver Binding and related protocols used in implementing UEFI driver model drivers. Each of these drivers supports more than one instance of a specific device can be in a system. Calls to Stop() and Start() will disable or enable the device and stop consumption of all system resources. This allows Super I/O drivers to be loaded and unloaded. These drivers can use the SIO Control protocol to enable consumption of system I/O and memory resources when they are started or stopped.

14.2. Code Definitions¶

14.2.1. EFI_SIO_PPI¶

Summary

Super I/O register access.

GUID

#define EFI_SIO_PPI_GUID \

{0x23a464ad, 0xcb83, 0x48b8, \

{0x94, 0xab, 0x1a, 0x6f, 0xef, 0xcf, 0xe5, 0x22}}

Protocol Interface Structure

typedef struct _EFI_SIO_PPI {

EFI_PEI_SIO_REGISTER_READ Read;

EFI_PEI_SIO_REGISTER_WRITE Write;

EFI_PEI_SIO_REGISTER_MODIFY Modify;

EFI_GUID SioGuid;

PEFI_SIO_INFO Info;

} EFI_SIO_PPI, *PEFI_SIO_PPI;

Members

- Read

This function reads a register’s value from the Super I/O controller.

- Write

This function writes a value to a register in the Super I/O controller.

- Modify

This function modifies zero or more registers in the Super I/O controller using a table.

- SioGuid

This GUID uniquely identifies the Super I/O controller.

- Info

This pointer is to an array which maps EISA identifiers to logical devices numbers.

Description

This PPI provides low-level access to Super I/O registers using Read() and Write() . It also uniquely identifies this Super I/O controller using a GUID and provides mappings between ACPI-style PNP IDs and the logical device numbers. There is one instance of this PPI per Super I/O device.

This PPI is produced by the Super I/O PEIM after the driver has determined that it is present in the system.

typedef struct _EFI_SIO_INFO {

EFI_ACPI_HID Hid;

EFI_ACPI_UID Uid;

UINT8 Ldn;

} EFI_SIO_INFO, *PEFI_SIO_INFO;

Hid

This is the EISA-style Plug-and-Play identifier for one of the devices on the super I/O controller. The standard values are:

- Uid

This is the unique zero-based instance number for a device on the super I/O. For example, if there are two serial ports, one of them would have a Uid of 0 and the other would have a Uid of 1.

- Ldn

This is the Logical Device Number for this logical device in the Super I/O. This value can be used in the Read() and Write() functions. The logical device number of EFI_SIO_LDN_GLOBAL indicates that global registers will be used.

typedef UINT32 EFI_ACPI_HID;

typedef UINT32 EFI_ACPI_UID;

#define EFI_ACPI_PNP_HID_KBC EFI_PNP_ID(0x0303)

#define EFI_ACPI_PNP_HID_LPT EFI_PNP_ID(0x0400)

#define EFI_ACPI_PNP_HID_COM EFI_PNP_ID(0x0500)

#define EFI_ACPI_PNP_HID_FDC EFI_PNP_ID(0x0700)

#define EFI_ACPI_PNP_HID_MIDI EFI_PNP_ID(0xB006)

#define EFI_ACPI_PNP_HID_END EFI_PNP_ID(0x0000)

#define EFI_ACPI_PNP_HID_GAME EFI_PNP_ID(0xB02F)

#pragma pack(1)

typedef struct _EFI_SIO_INFO {

EFI_ACPI_HID Hid;

EFI_ACPI_UID Uid;

UINT8 Ldn;

} EFI_SIO_INFO, *PEFI_SIO_INFO;

#pragma pack()

14.2.1.1. EFI_SIO_PPI.Read()¶

Prototype

typedef

EFI_STATUS

(EFIAPI \*EFI_PEI_SIO_REGISTER_READ) (

IN EFI_PEI_SERVICES **PeiServices,

IN CONST EFI_SIO_PPI *This,

IN BOOLEAN ExitCfgMode,

IN EFI_SIO_REGISTER Register,

OUT UINT8 *IoData

);

Parameters

- PeiServices

A pointer to a pointer to the PEI Services.

- This

A pointer to this instance of the EFI_SIO_PPI .

- ExitCfgMode

A boolean specifying whether the driver should turn on configuration mode (FALSE) or turn off configuration mode (TRUE) after completing the read operation. The driver must track the current state of the configuration mode (if any) and turn on configuration mode (if necessary) prior to register access.

- Register

A value specifying the logical device number (bits 15:8) and the register to read (bits 7:0). The logical device number of EFI_SIO_LDN_GLOBAL indicates that global registers will be used.

- IoData

A pointer to the returned register value.

Description

This function provides low-level read access to a device register. The register is specified as an 8-bit logical device number and an 8-bit register value. The logical device numbers for specific SIO devices can be determined using the Info member of the PPI structure.

If this function completes successfully, it will return EFI_SUCCESS and IoData will point to the returned Super I/O register value. If the register value was invalid for this device or IoData was NULL, then it will return EFI_INVALID_PARAMETERS . If the register could not be read within the correct amount of time, it will return EFI_TIMEOUT . If the device had some sort of fault or the device was not present, it will return EFI_DEVICE_ERROR .

Return Values

This function returns standard EFI status codes.

Status Code Value |

Description |

|---|---|

EFI_SUCCESS |

Success. |

EFI_TIMEOUT |

The register could not be read in a reasonable amount of time. The exact time is device-specific. |

EFI_INVALID_PARAMETERS |

Register was out of range for this device. IoData was NULL |

EFI_DEVICE_ERROR |

There was a device fault or the device was not present. |

Status Code Value |

Description |

EFI_SUCCESS |

Success. |

EFI_TIMEOUT |

The register could not be read in the a reasonable amount of time. The exact time is device-specific. |

EFI_INVALID_PARAMETERS |

Register was out of range for this device. IoData was NULL |

EFI_DEVICE_ERROR |

There was a device fault or the device was not present. |

typedef UINT16 EFI_SIO_REGISTER;

#define EFI_SIO_REG(ldn,reg) (EFI_SIO_REGISTER)(((ldn)<<8)|reg)

#define EFI_SIO_LDN_GLOBAL 0xFF

14.2.1.2. EFI_SIO_PPI.Write()¶

Write a Super I/O register.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PEI_SIO_REGISTER_WRITE) (

IN EFI_PEI_SERVICES **PeiServices,

IN CONST EFI_SIO_PPI *This,

IN BOOLEAN ExitCfgMode,

IN EFI_SIO_REGISTER Register,

IN UINT8 IoData

);

Parameters

- PeiServices

A pointer to a pointer to the PEI Services.

- This

A pointer to this instance of the EFI_SIO_PPI .

- ExitCfgMode

A boolean specifying whether the device should turn on configuration mode (FALSE) or turn off configuration mode (TRUE) after completing the write operation. The driver must track the current state of the configuration mode (if any) and turn on configuration mode (if necessary) prior to register access.

- Register

A value specifying the logical device number and the register to read. The logical device number can be determined by using the Super I/O chip specification or by looking up the value in the Info field of the EFI_SIO_PPI . The logical device number of EFI_SIO_LDN_GLOBAL indicates that global registers will be used.

- IoData

An 8-bit register value.

Status Code Return

Status Code Value |

Description |

|---|---|

EFI_SUCCESS |

Success. |

EFI_TIMEOUT |

The register could not be read in a reasonable amount of time. The exact time is device-specific. |

EFI_INVALID_PARAMETERS |

Register was out of range for this deive. IoData was NULL |

EFI_DEVICE_ERROR |

There was a device fault or ther device was not present. |

Description

This function provides low-level write access to a Super I/O register.

The register is specified as an 8-bit logical device number and an 8-bit register value. The logical device numbers for specific SIO devices can be determined using the Info member of the PPI structure.

If this function completes successfully, it will return EFI_SUCCESS and IoData will point to the returned Super I/O register value. If the register value was invalid for this device or IoData was NULL, then it will return EFI_INVALID_PARAMETERS . If the register could not be read within the correct amount of time, it will return EFI_TIMEOUT . If the device had some sort of fault or the device was not present, it will return EFI_DEVICE_ERROR .

14.2.1.3. EFI_SIO_PPI.Modify()¶

Summary

Provides an interface for a table based programming of the Super I/O registers.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_SIO_MODIFY)(

IN EFI_PEI_SERVICES **PeiServices,

IN CONST EFI_SIO_PPI *This,

IN CONST EFI_SIO_REGISTER_MODIFY *Command,

IN UINTN NumberOfCommands

);

Parameters

- PeiServices

A pointer to a pointer to the PEI Services.

- This

A pointer to this instance of the EFI_SIO_PPI .

- Command

A pointer to an array of NumberOfCommands EFI_SIO_REGISTER_MODIFY structures. Each structure specifies a single Super I/O register modify operation. Type EFI_SIO_REGISTER_MODIFY is defined in EFI_SIO_PROTOCOL.Modify() .

- NumberOfCommands

The number of elements in the Command array.

Description

The Modify() function provides an interface for table based programming of the Super I/O registers. This function can be used to perform programming of multiple Super I/O registers with a single function call. For each table entry, the Register is read, its content is bitwise ANDed with AndMask , and then ORed with OrMask before being written back to the Register . The Super I/O driver must track the current state of the Super I/O and enable the configuration mode of Super I/O if necessary prior to table processing. Once the table is processed, the Super I/O device must be returned to the original state.

Status Code Return

Status Code Value |

Description |

|---|---|

EFI_SUCCESS |

The operation completed successfully |

EFI_INVALID_PARAMETERS |

Command is NULL |

14.2.2. EFI_ISA_HC_PPI¶

GUID

#define EFI_ISA_HC_PPI_GUID \

{0x8d48bd70, 0xc8a3, 0x4c06, \

{0x90, 0x1b, 0x74, 0x79, 0x46, 0xaa, 0xc3, 0x58}}

PPI Structure

typedef struct _EFI_ISA_HC_PPI {

UINT32 Version;

UINT32 Address;

EFI_PEI_ISA_HC_OPEN_IO OpenIoAperture;

EFI_PEI_ISA_HC_CLOSE_IO CloseIoAperture;

} EFI_ISA_HC_PPI, \*PEFI_ISA_HC_PPI;

Members

- Version

An unsigned integer that specifies the version of the PPI structure. Initialized to zero.

- PciAddress

The address of the ISA/LPC Bridge device. For PCI, this is the segment, bus, device and function of the a ISA/LPC Bridge device.

If bits 24-31 are 0, then the definition is:

Bits 0:2 - FunctionBits 3-7 - DeviceBits 8:15 - BusBits 16-23 - SegmentBits 24-31 - Bus TypeIf bits 24-31 are 0xff, then the definition is platform-specific.

- OpenIoAperture

Opens an aperture on a positive-decode ISA Host Controller.

- CloseIoAperture

Closes an aperture on a positive-decode ISA Host Controller.

14.2.2.1. EFI_ISA_HC_PPI.OpenIoAperture()¶

Open I/O aperture.

Prototype

typedef

EFI_STATUS

(EFIAPI \*EFI_PEI_ISA_HC_OPEN_IO) (

IN CONST EFI_ISA_HC_PPI *This,

IN UINT16 IoAddress,

IN UINT16 IoLength,

OUT UINT64 *IoApertureHandle

);

Parameters

- PeiServices

A pointer to a pointer to the PEI Services Table.

- This

A pointer to this instance of the EFI_ISA_HC_PPI .

- IoAddress

An unsigned integer that specifies the first byte of the I/O space required.

- IoLength

An unsigned integer that specifies the number of bytes of the I/O space required.

- IoApertureHandle

A pointer to the returned I/O aperture handle. This value can be used on subsequent calls to CloseIoAperture() .

Description

This function opens an I/O aperture in a ISA Host Controller for the I/O addresses specified by IoAddress to IoAddress + IoLength - 1. It is possible that more than one caller may be assigned to the same aperture.

It may be possible that a single hardware aperture may be used for more than one device. This function tracks the number of times that each aperture is referenced, and doesa not close the hardware aperture (via CloseIoAperture() ) until there are no more references to it.

If this function completes successfully, then it returns EFI_SUCCESS . If there is no available I/O aperture, then this function returns EFI_OUT_OF_RESOURCES .

14.2.2.2. EFI_ISA_HC_PPI.CloseIoAperture()¶

Close I/O aperture.

Prototype

typedef

EFI_STATUS

(EFIAPI \*EFI_PEI_ISA_HC_CLOSE_IO) (

IN CONST EFI_ISA_HC_PPI *This,

IN UINT64 IoApertureHandle

);

Parameters

- PeiServices

A pointer to a pointer to the PEI Services Table.

- This

A pointer to this instance of the EFI_ISA_HC_PPI .

- IoApertureHandle

The I/O aperture handle previously returned from a call to OpenIoAperture() .

Description

This function closes a previously opened I/O aperture handle. If there are no more I/O aperture handles that refer to the hardware I/O aperture resource, then the hardware I/O aperture is closed.

It may be possible that a single hardware aperture may be used for more than one device. This function tracks the number of times that each aperture is referenced, and does not close the hardware aperture (via CloseIoAperture() ) until there are no more references to it.

14.2.3. EFI_ISA_HC_PROTOCOL¶

Summary

Provides registration and enumeration of ISA devices.

GUID

#define EFI_ISA_HC_PROTOCOL_GUID \

{0xbcdaf080, 0x1bde, 0x4e22, \

{0xae, 0x6a, 0x43, 0x54, 0x1e, 0x12, 0x8e, 0xc4}}

Protocol Interface Structure

typedef struct _EFI_ISA_HC_PROTOCOL {

UINT32 Version;

EFI_ISA_HC_OPEN_IO OpenIoAperture;

EFI_ISA_HC_CLOSE_IO CloseIoAperture;

} EFI_ISA_HC_PROTOCOL, *PEFI_ISA_HC_PROTOCOL;

Members

- Version

The version of this protocol. Higher version numbers are backward compatible with lower version numbers. The current version is 0.

- OpenIoAperture

Open an I/O aperture.

- CloseIoAperture

Close an I/O aperture.

Description

This protocol provides registration for ISA devices on a positive- or subtractive-decode ISA bus. It allows devices to be registered and also handles opening and closing the apertures which are positively-decoded.

14.2.3.1. EFI_ISA_HC_PROTOCOL.OpenIoAperture()¶

Open I/O aperture.

Prototype

typedef

EFI_STATUS

(EFIAPI \*EFI_ISA_HC_OPEN_IO) (

IN CONST EFI_ISA_HC_PROTOCOL *This,

IN UINT16 IoAddress,

IN UINT16 IoLength,

OUT UINT64 *IoApertureHandle

);

Parameters

- This

A pointer to this instance of the EFI_ISA_HC_PROTOCOL .

- IoAddress

An unsigned integer that specifies the first byte of the I/O space required.

- IoLength

An unsigned integer that specifies the number of bytes of the I/O space required.

- IoApertureHandle

A pointer to the returned I/O aperture handle. This value can be used on subsequent calls to CloseIoAperture() .

Description

This function opens an I/O aperture in a ISA Host Controller for the I/O addresses specified by IoAddress to IoAddress + IoLength - 1.

It may be possible that a single hardware aperture may be used for more than one device. This function tracks the number of times that each aperture is referenced, and does not close the hardware aperture (via CloseIoAperture() ) until there are no more references to it.

If this function completes successfully, then it returns EFI_SUCCESS . If there is no available I/O aperture, then this function returns EFI_OUT_OF_RESOURCES .

14.2.3.2. EFI_ISA_HC_PROTOCOL.CloseIoAperture()¶

Close I/O aperture.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_ISA_HC_CLOSE_IO) (

IN CONST EFI_ISA_HC_PROTOCOL *This,

IN UINT64 IoApertureHandle

);

Parameters

- PeiServices

A pointer to a pointer to the PEI Services Table.

- This

A pointer to this instance of the EFI_ISA_HC_PROTOCOL .

- IoApertureHandle

The I/O aperture handle previously returned from a call to OpenIoAperture() .

Description

This function closes a previously opened I/O aperture handle. If there are no more I/O aperture handles that refer to the hardware I/O aperture resource, then the hardware I/O aperture is closed.

It may be possible that a single hardware aperture may be used for more than one device. This function tracks the number of times that each aperture is referenced, and does not close the hardware aperture (via CloseIoAperture() ) until there are no more references to it.

14.2.4. EFI_ISA_HC_SERVICE_BINDING_PROTOCOL¶

Summary

Manages child devices for an ISA Host Controller.

GUID

#define EFI_ISA_HC_SERVICE_BINDING_PROTOCOL_GUID \

{0xfad7933a, 0x6c21, 0x4234, \

{0xa4, 0x34, 0x0a, 0x8a, 0x0d, 0x2b, 0x07, 0x81}}

Protocol Interface Structure

The protocol interface structure is the same for all service binding protocols and can be found in Section 10.6 (“EFI Service Binding Protocol”).

Description

The ISA Host Controller Service Binding protocol permits multiple Super I/O devices to use the services provide by an ISA Host Controller. The function CreateChild() installs an instance of the ISA Host Controller protocol on each child handle created.

14.2.5. EFI_SIO_CONTROL_PROTOCOL¶

Summary

Provide low-level services for SIO devices that enable them to be used in the UEFI driver model.

GUID

#define EFI_SIO_CONTROL_PROTOCOL_GUID \

{0xb91978df, 0x9fc1, 0x427d, \

{0xbb, 0x5, 0x4c, 0x82, 0x84, 0x55, 0xca, 0x27}}

Protocol Interface Structure

typedef struct _EFI_SIO_CONTROL_PROTOCOL {

UINT32 Version;

EFI_SIO_CONTROL_ENABLE EnableDevice;

EFI_SIO_CONTROL_DISABLE DisableDevice;

} EFI_SIO_CONTROL_PROTOCOL, PEFI_SIO_CONTROL_PROTOCOL;

Members

- Version

The version of this protocol. Higher version numbers are backward compatible with lower version numbers. The current version is 0.

- EnableDevice

Enable a device.

- DisableDevice

Disable a device.

Description

The EFI_SIO_CONTROL_PROTOCOL provides control over the decoding of Super I/O and memory resources by a logical device within a Super I/O. While the logical devices often implement industry standard interfaces (such as PS/2 keyboard or serial port), these standard interfaces do not describe how to enable or disable the memory and I/O resources for those devices. Instead, this control is usually implemented within the Super I/O device itself through proprietary means. The industry standard drivers may utilize these functions in their implementations of the Driver Binding protocol’s Start() and Stop() functions.

The Super I/O driver installs this protocol on the same child handle as the EFI_SIO_PROTOCOL .

14.2.5.1. EFI_SIO_CONTROL_PROTOCOL.Enable()¶

Summary

Enable an ISA-style device.

Prototype

typedef

EFI_STATUS

(EFIAPI \*EFI_SIO_CONTROL_ENABLE)(

IN CONST EFI_SIO_CONTROL_PROTOCOL *This

);

Parameters

- This

A pointer to this instance of the EFI_SIO_CONTROL_PROTOCOL .

Description

This function enables a logical ISA device and, if necessary, configures it to default settings, including memory, I/O, DMA and IRQ resources.

If the function completed successfully, then this function returns EFI_SUCCESS .

If the device could not be enabled because there were insufficient resources either for the device itself or for the records needed to track the device, then this function returns EFI_OUT_OF_RESOURCES .

If this device is already enabled, then this function returns EFI_ALREADY_STARTED . If this device cannot be enabled, then this function returns EFI_UNSUPPORTED .

14.2.5.2. EFI_SIO_CONTROL_PROTOCOL.Disable()¶

Summary

Disable a logical ISA device.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_SIO_CONTROL_DISABLE)(

IN CONST EFI_SIO_CONTROL_PROTOCOL *This

);

Parameters

- This

A pointer to this instance of the EFI_SIO_CONTROL_PROTOCOL .

Description

This function disables a logical ISA device so that it no longer consumes system resources, such as memory, I/O, DMA and IRQ resources. Enough information must be available so that subsequent Enable() calls would properly reconfigure the device.

If this function completed successfully, then it returns EFI_SUCCESS .

If the device could not be disabled because there were insufficient resources either for the device itself or for the records needed to track the device, then this function returns EFI_OUT_OF_RESOURCES .

If this device is already disabled, then this function returns EFI_ALREADY_STARTED . If this device cannot be disabled, then this function returns EFI_UNSUPPORTED .