14. Protocols — PCI Bus Support

14.1. PCI Root Bridge I/O Support

This section and the following one (Section 14.2) describe the PCI Root Bridge I/O Protocol. This protocol provides an I/O abstraction for a PCI Root Bridge that is produced by a PCI Host Bus Controller. A PCI Host Bus Controller is a hardware component that allows access to a group of PCI devices that share a common pool of PCI I/O and PCI Memory resources. This protocol is used by a PCI Bus Driver to perform PCI Memory, PCI I/O, and PCI Configuration cycles on a PCI Bus. It also provides services to perform different types of bus mastering DMA on a PCI bus. PCI device drivers will not directly use this protocol. Instead, they will use the I/O abstraction produced by the PCI Bus Driver. Only drivers that require direct access to the entire PCI bus should use this protocol. In particular, this chapter defines functions for managing PCI buses, although other bus types may be supported in a similar fashion as extensions to this specification.

All the services described in this chapter that generate PCI transactions follow the ordering rules defined in the PCI Specification. If the processor is performing a combination of PCI transactions and system memory transactions, then there is no guarantee that the system memory transactions will be strongly ordered with respect to the PCI transactions. If strong ordering is required, then processor-specific mechanisms may be required to guarantee strong ordering. Some 64-bit systems may require the use of memory fences to guarantee ordering.

14.1.1. PCI Root Bridge I/O Overview

The interfaces provided in the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL are for performing basic operations to memory, I/O, and PCI configuration space. The system provides abstracted access to basic system resources to allow a driver to have a programmatic method to access these basic system resources.

The EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL allows for future innovation of the platform. It abstracts device-specific code from the system memory map. This allows system designers to make changes to the system memory map without impacting platform independent code that is consuming basic system resources.

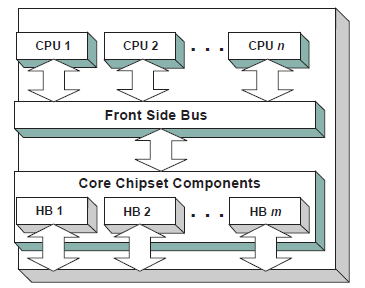

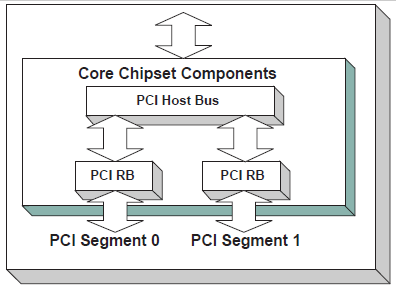

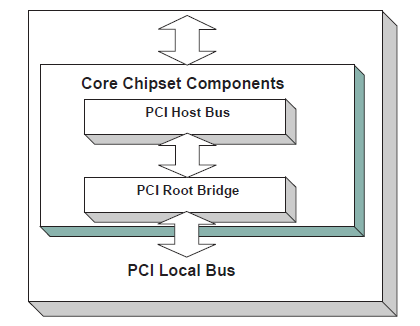

A platform can be viewed as a set of processors and a set of core chipset components that may produce one or more host buses. Figure Host Bus Controllers shows a platform with n processors (CPUs in the figure), and a set of core chipset components that produce m host bridges.

Fig. 14.1 Host Bus Controllers

Simple systems with one PCI Host Bus Controller will contain a single instance of the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. More complex system may contain multiple instances of this protocol. It is important to note that there is no relationship between the number of chipset components in a platform and the number of EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL instances. This protocol abstracts access to a PCI Root Bridge from a software point of view, and it is attached to a device handle that represents a PCI Root Bridge. A PCI Root Bridge is a chipset component(s) that produces a physical PCI Bus. It is also the parent to a set of PCI devices that share common PCI I/O, PCI Memory, and PCI Prefetchable Memory regions. A PCI Host Bus Controller is composed of one or more PCI Root Bridges.

A PCI Host Bridge and PCI Root Bridge are different than a PCI Segment. A PCI Segment is a collection of up to 256 PCI busses that share the same PCI Configuration Space. Depending on the chipset, a single EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL may abstract a portion of a PCI Segment, or an entire PCI Segment. A PCI Host Bridge may produce one or more PCI Root Bridges. When a PCI Host Bridge produces multiple PCI Root Bridges, it is possible to have more than one PCI Segment.

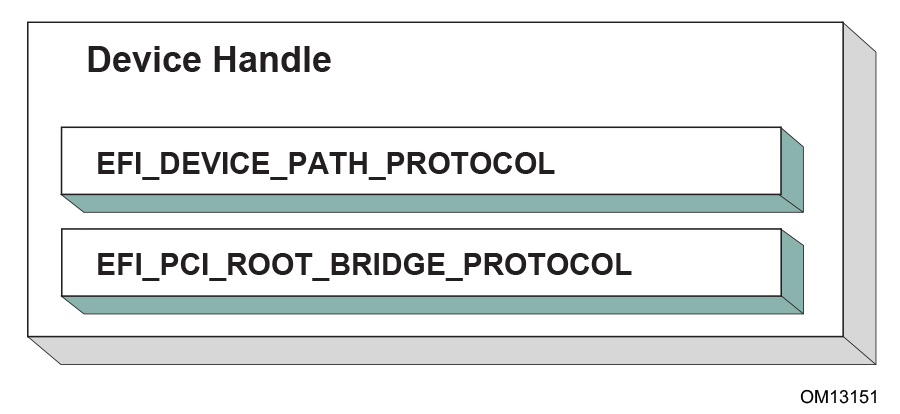

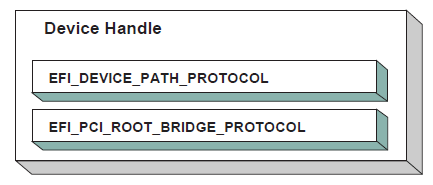

PCI Root Bridge I/O Protocol instances are either produced by the system firmware or by a UEFI driver. When a PCI Root Bridge I/O Protocol is produced, it is placed on a device handle along with an EFI Device Path Protocol instance. The figure below (Device Handle for a PCI Root Bridge Controller) shows a sample device handle that includes an instance of the EFI_DEVICE_PATH_PROTOCOL and the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.

Section Section 14.2 describes the PCI Root Bridge I/O Protocol in detail, and Section 14.2.19 describes how to build device paths for PCI Root Bridges. The EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL does not abstract access to the chipset-specific registers used to manage a PCI Root Bridge. This functionality is hidden within the system firmware or the driver that produces the handles that represent the PCI Root Bridges.

Fig. 14.2 Device Handle for a PCI Root Bridge Controller

14.1.2. Sample PCI Architectures

The PCI Root Bridge I/O Protocol is designed to provide a software abstraction for a wide variety of PCI architectures including the ones described in this section. This section is not intended to be an exhaustive list of the PCI architectures that the PCI Root Bridge I/O Protocol can support. Instead, it is intended to show the flexibility of this protocol to adapt to current and future platform designs.

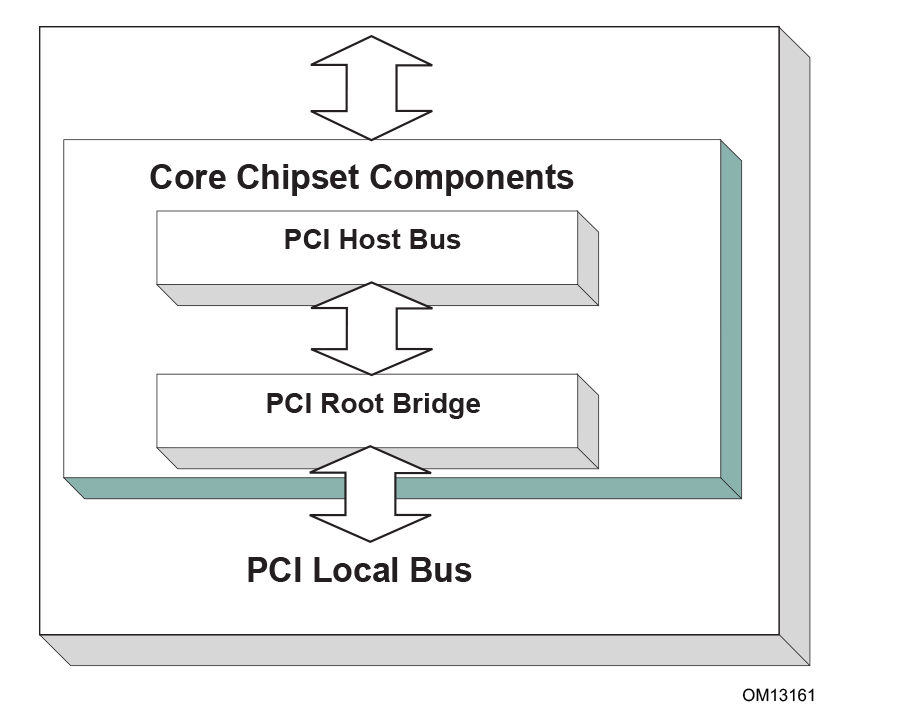

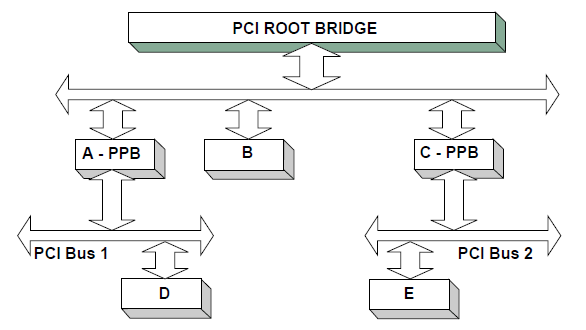

See Desktop System with One PCI Root Bridge shows an example of a PCI Host Bus with one PCI Root Bridge. This PCI Root Bridge produces one PCI Local Bus that can contain PCI Devices on the motherboard and/or PCI slots. This would be typical of a desktop system. A higher end desktop system might contain a second PCI Root Bridge for AGP devices. The firmware for this platform would produce one instance of the PCI Root Bridge I/O Protocol.

Fig. 14.3 Desktop System with One PCI Root Bridge

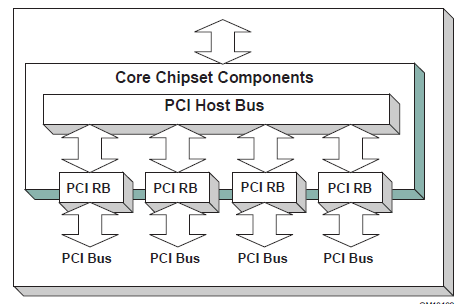

Figure Server System with Four PCI Root Bridges shows an example of a larger server with one PCI Host Bus and four PCI Root Bridges. The PCI devices attached to the PCI Root Bridges are all part of the same coherency domain. This means they share a common PCI I/O Space, a common PCI Memory Space, and a common PCI Prefetchable Memory Space. Each PCI Root Bridge produces one PCI Local Bus that can contain PCI Devices on the motherboard or PCI slots. The firmware for this platform would produce four instances of the PCI Root Bridge I/O Protocol.

Fig. 14.4 Server System with Four PCI Root Bridges

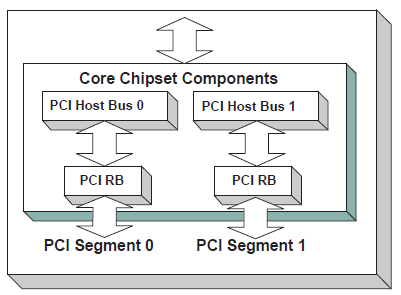

The Figure Server System with Two PCI Segments , below, shows an example of a server with one PCI Host Bus and two PCI Root Bridges. Each of these PCI Root Bridges is a different PCI Segment which allows the system to have up to 512 PCI Buses. A single PCI Segment is limited to 256 PCI Buses. These two segments do not share the same PCI Configuration Space, but they do share the same PCI I/O, PCI Memory, and PCI Prefetchable Memory Space. This is why it can be described by a single PCI Host Bus. The firmware for this platform would produce two instances of the PCI Root Bridge I/O Protocol.

Fig. 14.5 Server System with Two PCI Segments

The Figure, Server System with Two PCI Host Buses , below, shows a server system with two PCI Host Buses and one PCI Root Bridge per PCI Host Bus. This system supports up to 512 PCI Buses, but the PCI I/O, PCI Memory Space, and PCI Prefetchable Memory Space are not shared between the two PCI Root Bridges. The firmware for this platform would produce two instances of the PCI Root Bridge I/O Protocol.

Fig. 14.6 Server System with Two PCI Host Buses

14.2. PCI Root Bridge I/O Protocol

This section provides detailed information on the PCI Root Bridge I/O Protocol and its functions.

14.2.1. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL

Summary

Provides the basic Memory, I/O, PCI configuration, and DMA interfaces that are used to abstract accesses to PCI controllers behind a PCI Root Bridge Controller.

GUID

#define EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_GUID \

{0x2F707EBB,0x4A1A,0x11d4,\

{0x9A,0x38,0x00,0x90,0x27,0x3F,0xC1,0x4D}}

Protocol Interface Structure

typedef struct _EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL {

EFI_HANDLE

ParentHandle;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_POLL_IO_MEM PollMem;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_POLL_IO_MEM PollIo;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_ACCESS Mem;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_ACCESS Io;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_ACCESS Pci;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_COPY_MEM CopyMem;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_MAP Map;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_UNMAP Unmap;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_ALLOCATE_BUFFER AllocateBuffer;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_FREE_BUFFER FreeBuffer;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_FLUSH Flush;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_GET_ATTRIBUTES GetAttributes;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_SET_ATTRIBUTES SetAttributes;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_CONFIGURATION Configuration;

UINT32 SegmentNumber;

} EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL;

Parameters

- ParentHandle

The EFI_HANDLE of the PCI Host Bridge of which this PCI Root Bridge is a member.

- PollMem

Polls an address in memory mapped I/O space until an exit condition is met, or a timeout occurs. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.PollMem() function description .

- PollIo

Polls an address in I/O space until an exit condition is met, or a timeout occurs. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.PollIo() function description.

- Mem.Read

Allows reads from memory mapped I/O space. See the Mem.Read() EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Mem.Read() function description.

- Mem.Write

Allows writes to memory mapped I/O space. See the Mem.Write() EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Mem.Write() function description.

- Io.Read

Allows reads from I/O space. See the Io.Read() EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Io.Read() function description.

- Io.Write

Allows writes to I/O space. See the Io.Write() EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Io.WRITE() function description.

- Pci.Read

Allows reads from PCI configuration space. See the Pci.Read() EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Pci.Read() function description.

- Pci.Write

Allows writes to PCI configuration space. See the Pci.Write() EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Pci.Write() function description.

- CopyMem

Allows one region of PCI root bridge memory space to be copied to another region of PCI root bridge memory space. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.CopyMem() function description.

- Map

Provides the PCI controller-specific addresses needed to access system memory for DMA. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map() function description.

- Unmap

Releases any resources allocated by Map(). See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Unmap() function description.

- AllocateBuffer

Allocates pages that are suitable for a common buffer mapping. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.AllocateBuffer() function description.

- FreeBuffer

Free pages that were allocated with AllocateBuffer(). See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.FreeBuffer() function description.

- Flush

Flushes all PCI posted write transactions to system memory. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Flush() function description.

- GetAttributes

Gets the attributes that a PCI root bridge supports setting with EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.SetAttributes() , and the attributes that a PCI root bridge is currently using. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.GetAttributes() function description.

- SetAttributes

Sets attributes for a resource range on a PCI root bridge. See EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.SetAttributes() function description.

- Configuration

Gets the current resource settings for this PCI root bridge. See the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Configuration() function description.

- SegmentNumber

The segment number that this PCI root bridge resides.

Related Definitions

//******************************************************

// EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH

//******************************************************

typedef enum {

EfiPciWidthUint8,

EfiPciWidthUint16,

EfiPciWidthUint32,

EfiPciWidthUint64,

EfiPciWidthFifoUint8,

EfiPciWidthFifoUint16,

EfiPciWidthFifoUint32,

EfiPciWidthFifoUint64,

EfiPciWidthFillUint8,

EfiPciWidthFillUint16,

EfiPciWidthFillUint32,

EfiPciWidthFillUint64,

EfiPciWidthMaximum

} EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH;

//******************************************************

// EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_POLL_IO_MEM

//******************************************************

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_POLL_IO_MEM) (

IN struct EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 Address,

IN UINT64 Mask,

IN UINT64 Value,

IN UINT64 Delay,

OUT UINT64 *Result

);

//******************************************************

// EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_IO_MEM

//******************************************************

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_IO_MEM) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 Address,

IN UINTN Count,

IN OUT VOID *Buffer

);

//******************************************************

// EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_ACCESS

//******************************************************

typedef struct {

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_IO_MEM Read;

EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_IO_MEM Write;

} EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_ACCESS;

//******************************************************

// EFI PCI Root Bridge I/O Protocol Attribute bits

//******************************************************

#define EFI_PCI_ATTRIBUTE_ISA_MOTHERBOARD_IO 0x0001

#define EFI_PCI_ATTRIBUTE_ISA_IO 0x0002

#define EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO 0x0004

#define EFI_PCI_ATTRIBUTE_VGA_MEMORY 0x0008

#define EFI_PCI_ATTRIBUTE_VGA_IO 0x0010

#define EFI_PCI_ATTRIBUTE_IDE_PRIMARY_IO 0x0020

#define EFI_PCI_ATTRIBUTE_IDE_SECONDARY_IO 0x0040

#define EFI_PCI_ATTRIBUTE_MEMORY_WRITE_COMBINE 0x0080

#define EFI_PCI_ATTRIBUTE_MEMORY_CACHED 0x0800

#define EFI_PCI_ATTRIBUTE_MEMORY_DISABLE 0x1000

#define EFI_PCI_ATTRIBUTE_DUAL_ADDRESS_CYCLE 0x8000

#define EFI_PCI_ATTRIBUTE_ISA_IO_16 0x10000

#define EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO_16 0x20000

#define EFI_PCI_ATTRIBUTE_VGA_IO_16 0x40000

- EFI_PCI_ATTRIBUTE_ISA_IO_16

If this bit is set, then the PCI I/O cycles between 0x100 and 0x3FF are forwarded onto a PCI root bridge using a 16-bit address decoder on address bits 0..15. Address bits 16..31 must be zero. This bit is used to forward I/O cycles for legacy ISA devices onto a PCI root bridge. This bit may not be combined with EFI_PCI_ATTRIBUTE_ISA_IO.

- EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO_16

If this bit is set, then the PCI I/O write cycles for 0x3C6, 0x3C8, and 0x3C9 are forwarded onto a PCI root bridge using a 16-bit address decoder on address bits 0..15. Address bits 16..31 must be zero. This bit is used to forward I/O write cycles to the VGA palette registers onto a PCI root bridge. This bit may not be combined with EFI_PCI_ATTRIBUTE_VGA_IO or EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO.

- EFI_PCI_ATTRIBUTE_VGA_IO_16

If this bit is set, then the PCI I/O cycles in the ranges 0x3B0-0x3BB and 0x3C0-0x3DF are forwarded onto a PCI root bridge using a 16-bit address decoder on address bits 0..15. Address bits 16..31 must be zero. This bit is used to forward I/O cycles for a VGA controller onto a PCI root bridge. This bit may not be combined with EFI_PCI_ATTRIBUTE_VGA_IO or EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO. Because EFI_PCI_ATTRIBUTE_VGA_IO_16 also includes the I/O range described by EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO_16 , the EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO_16 bit is ignored if EFI_PCI_ATTRIBUTE_VGA_IO_16 is set.

- EFI_PCI_ATTRIBUTE_ISA_MOTHERBOARD_IO

If this bit is set, then the PCI I/O cycles between 0x00000000 and 0x000000FF are forwarded onto a PCI root bridge. This bit is used to forward I/O cycles for ISA motherboard devices onto a PCI root bridge.

- EFI_PCI_ATTRIBUTE_ISA_IO

If this bit is set, then the PCI I/O cycles between 0x100 and 0x3FF are forwarded onto a PCI root bridge using a 10-bit address decoder on address bits 0..9. Address bits 10..15 are not decoded, and address bits 16..31 must be zero. This bit is used to forward I/O cycles for legacy ISA devices onto a PCI root bridge.

- EFI_PCI_ATTRIBUTE_VGA_PALETTE_IO

If this bit is set, then the PCI I/O write cycles for 0x3C6, 0x3C8, and 0x3C9 are forwarded onto a PCI root bridge using a 10 bit address decoder on address bits 0..9. Address bits 10..15 are not decoded, and address bits 16..31 must be zero. This bit is used to forward I/O write cycles to the VGA palette registers onto a PCI root bridge.

- EFI_PCI_ATTRIBUTE_VGA_MEMORY

If this bit is set, then the PCI memory cycles between 0xA0000 and 0xBFFFF are forwarded onto a PCI root bridge. This bit is used to forward memory cycles for a VGA frame buffer onto a PCI root bridge.

- EFI_PCI_ATTRIBUTE_VGA_IO

If this bit is set, then the PCI I/O cycles in the ranges 0x3B0-0x3BB and 0x3C0-0x3DF are forwarded onto a PCI root bridge using a 10-bit address decoder on address bits 0..9. Address bits 10..15 are not decoded, and the address bits 16..31 must be zero. This bit is used to forward I/O cycles for a VGA controller onto a PCI root bridge. Since EFI_PCI_ATTRIBUTE_ENABLE_VGA_IO also includes the I/O range described by EFI_PCI_ATTRIBUTE_ENABLE_VGA_PALETTE_IO, the EFI_PCI_ATTRIBUTE_ENABLE_VGA_PALETTE_IO bit is ignored if EFI_PCI_ATTRIBUTE_ENABLE_VGA_IO is set.

- EFI_PCI_ATTRIBUTE_IDE_PRIMARY_IO

If this bit is set, then the PCI I/O cycles in the ranges 0x1F0-0x1F7 and 0x3F6-0x3F7 are forwarded onto a PCI root bridge using a 16-bit address decoder on address bits 0..15. Address bits 16..31 must be zero. This bit is used to forward I/O cycles for a Primary IDE controller onto a PCI root bridge.

- EFI_PCI_ATTRIBUTE_IDE_SECONDARY_IO

If this bit is set, then the PCI I/O cycles in the ranges 0x170-0x177 and 0x376-0x377 are forwarded onto a PCI root bridge using a 16-bit address decoder on address bits 0..15. Address bits 16..31 must be zero. This bit is used to forward I/O cycles for a Secondary IDE controller onto a PCI root bridge.

- EFI_PCI_ATTRIBUTE_MEMORY_WRITE_COMBINE

If this bit is set, then this platform supports changing the attributes of a PCI memory range so that the memory range is accessed in a write combining mode. By default, PCI memory ranges are not accessed in a write combining mode.

- EFI_PCI_ATTRIBUTE_MEMORY_CACHED

If this bit is set, then this platform supports changing the attributes of a PCI memory range so that the memory range is accessed in a cached mode. By default, PCI memory ranges are accessed noncached.

- EFI_PCI_ATTRIBUTE_MEMORY_DISABLE

If this bit is set, then this platform supports changing the attributes of a PCI memory range so that the memory range is disabled, and can no longer be accessed. By default, all PCI memory ranges are enabled.

- EFI_PCI_ATTRIBUTE_DUAL_ADDRESS_CYCLE

This bit may only be used in the Attributes parameter to EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.AllocateBuffer(). If this bit is set, then the PCI controller that is requesting a buffer through AllocateBuffer() is capable of producing PCI Dual Address Cycles, so it is able to access a 64-bit address space. If this bit is not set, then the PCI controller that is requesting a buffer through AllocateBuffer() is not capable of producing PCI Dual Address Cycles, so it is only able to access a 32-bit address space.

//******************************************************

// EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_OPERATION

//******************************************************

typedef enum {

EfiPciOperationBusMasterRead,

EfiPciOperationBusMasterWrite,

EfiPciOperationBusMasterCommonBuffer,

EfiPciOperationBusMasterRead64,

EfiPciOperationBusMasterWrite64,

EfiPciOperationBusMasterCommonBuffer64,

EfiPciOperationMaximum

} EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_OPERATION;

- EfiPciOperationBusMasterRead

A read operation from system memory by a bus master that is not capable of producing PCI dual address cycles.

- EfiPciOperationBusMasterWrite

A write operation to system memory by a bus master that is not capable of producing PCI dual address cycles.

- EfiPciOperationBusMasterCommonBuffer

Provides both read and write access to system memory by both the processor and a bus master that is not capable of producing PCI dual address cycles. The buffer is coherent from both the processor’s and the bus master’s point of view.

- EfiPciOperationBusMasterRead64

A read operation from system memory by a bus master that is capable of producing PCI dual address cycles.

- EfiPciOperationBusMasterWrite64

A write operation to system memory by a bus master that is capable of producing PCI dual address cycles.

- EfiPciOperationBusMasterCommonBuffer64

Provides both read and write access to system memory by both the processor and a bus master that is capable of producing PCI dual address cycles. The buffer is coherent from both the processor’s and the bus master’s point of view.

Description

The EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL provides the basic Memory, I/O, PCI configuration, and DMA interfaces that are used to abstract accesses to PCI controllers. There is one EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL instance for each PCI root bridge in a system. Embedded systems, desktops, and workstations will typically only have one PCI root bridge. High-end servers may have multiple PCI root bridges. A device driver that wishes to manage a PCI bus in a system will have to retrieve the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL instance that is associated with the PCI bus to be managed. A device handle for a PCI Root Bridge will minimally contain an EFI Device Path Protocol instance and an EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL instance. The PCI bus driver can look at the EFI_DEVICE_PATH_PROTOCOL instances to determine which EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL instance to use.

Bus mastering PCI controllers can use the DMA services for DMA operations. There are three basic types of bus mastering DMA that is supported by this protocol. These are DMA reads by a bus master, DMA writes by a bus master, and common buffer DMA. The DMA read and write operations may need to be broken into smaller chunks. The caller of EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map() must pay attention to the number of bytes that were mapped, and if required, loop until the entire buffer has been transferred. The following is a list of the different bus mastering DMA operations that are supported, and the sequence of EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL APIs that are used for each DMA operation type. See “Related Definitions” above for the definition of the different DMA operation types.

DMA Bus Master Read Operation

Call EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map() for EfiPciOperationBusMasterRead or EfiPciOperationBusMasterRead64.

Program the DMA Bus Master with the DeviceAddress returned by Map().

Start the DMA Bus Master.

Wait for DMA Bus Master to complete the read operation.

DMA Bus Master Write Operation

Call EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map() for EfiPciOperationBusMasterWrite or EfiPciOperationBusMasterRead64.

Program the DMA Bus Master with the DeviceAddress returned by EFI_PCI_IO_PROTOCOL.Map()

Start the DMA Bus Master.

Wait for DMA Bus Master to complete the write operation.

Perform a PCI controller specific read transaction to flush all PCI write buffers (See PCI Specification Section 3.2.5.2).

Call Unmap.

DMA Bus Master Common Buffer Operation

Call EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.AllocateBuffer() to allocate a common buffer.

Call Map() for EfiPciOperationBusMasterCommonBuffer or EfiPciOperationBusMasterCommonBuffer64.

Program the DMA Bus Master with the DeviceAddress returned by EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map() .

The common buffer can now be accessed equally by the processor and the DMA bus master.

Call Unmap().

14.2.2. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.PollMem()

Summary

Reads from the memory space of a PCI Root Bridge. Returns when either the polling exit criteria is satisfied or after a defined duration.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_POLL_IO_MEM) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 Address,

IN UINT64 Mask,

IN UINT64 Value,

IN UINT64 Delay,

OUT UINT64 *Result

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in the Section PCI Root Bridge I/O Protocol .

- Width

Signifies the width of the memory operations. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH see Related Definitions in the section EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL .

- Address

The base address of the memory operations. The caller is responsible for aligning Address if required.

- Mask

Mask used for the polling criteria. Bytes above Width in Mask are ignored. The bits in the bytes below Width which are zero in Mask are ignored when polling the memory address.

- Value

The comparison value used for the polling exit criteria.

- Delay

The number of 100 ns units to poll. Note that timer available may be of poorer granularity.

- Result

Pointer to the last value read from the memory location.

Description

This function provides a standard way to poll a PCI memory location. A PCI memory read operation is performed at the PCI memory address specified by Address for the width specified by Width. The result of this PCI memory read operation is stored in Result. This PCI memory read operation is repeated until either a timeout of Delay 100 ns units has expired, or ( Result & Mask) is equal to Value.

This function will always perform at least one PCI memory read access no matter how small Delay may be. If Delay is zero, then Result will be returned with a status of EFI_SUCCESS even if Result does not match the exit criteria. If Delay expires, then EFI_TIMEOUT is returned.

If Width is not EfiPciWidthUint8 , EfiPciWidthUint16 , EfiPciWidthUint32 , or EfiPciWidthUint64 , then EFI_INVALID_PARAMETER is returned.

The memory operations are carried out exactly as requested. The caller is responsible for satisfying any alignment and memory width restrictions that a PCI Root Bridge on a platform might require. For example on some platforms, width requests of EfiPciWidthUint64 are not supported.

All the PCI transactions generated by this function are guaranteed to be completed before this function returns. However, if the memory mapped I/O region being accessed by this function has the EFI_PCI_ATTRIBUTE_MEMORY_CACHED attribute set, then the transactions will follow the ordering rules defined by the processor architecture.

Status Codes Returned

EFI_SUCCESS |

The last data returned from the access matched the poll exit criteria. |

EFI_INVALID_PARAMETER |

Width is invalid. |

EFI_INVALID_PARAMETER |

Result is NULL. |

EFI_TIMEOUT |

Delay expired before a match occurred. |

EFI_OUT_OF_RESOURCES |

The request could not be completed due to a lack of resources. |

14.2.3. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.PollIo()

Summary

Reads from the I/O space of a PCI Root Bridge. Returns when either the polling exit criteria is satisfied or after a defined duration.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_POLL_IO_MEM) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 Address,

IN UINT64 Mask,

IN UINT64 Value,

IN UINT64 Delay,

OUT UINT64 *Result

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in PCI Root Bridge I/O Protocol .

- Width

Signifies the width of the I/O operations. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH see Related Definitions in the section PCI Root Bridge I/O Protocol .

- Address

The base address of the I/O operations. The caller is responsible for aligning Address if required.

- Mask

Mask used for the polling criteria. Bytes above Width in Mask are ignored. The bits in the bytes below Width which are zero in Mask are ignored when polling the I/O address.

- Value

The comparison value used for the polling exit criteria.

- Delay

The number of 100 ns units to poll. Note that timer available may be of poorer granularity.

- Result

Pointer to the last value read from the memory location.

Description

This function provides a standard way to poll a PCI I/O location. A PCI I/O read operation is performed at the PCI I/O address specified by Address for the width specified by Width. The result of this PCI I/O read operation is stored in Result. This PCI I/O read operation is repeated until either a timeout of Delay 100 ns units has expired, or ( Result & Mask ) is equal to Value.

This function will always perform at least one I/O access no matter how small Delay may be. If Delay is zero, then Result will be returned with a status of EFI_SUCCESS even if Result does not match the exit criteria. If Delay expires, then EFI_TIMEOUT is returned.

If Width is not EfiPciWidthUint8 , EfiPciWidthUint16 , EfiPciWidthUint32 , or EfiPciWidthUint64 , then EFI_INVALID_PARAMETER is returned.

The I/O operations are carried out exactly as requested. The caller is responsible satisfying any alignment and I/O width restrictions that the PCI Root Bridge on a platform might require. For example on some platforms, width requests of EfiPciWidthUint64 do not work.

All the PCI transactions generated by this function are guaranteed to be completed before this function returns.

Status Codes Returned

EFI_SUCCESS |

The last data returned from the access matched the poll exit criteria. |

EFI_INVALID_PARAMETER |

Width is invalid. |

EFI_INVALID_PARAMETER |

Result is NULL. |

EFI_TIMEOUT |

Delay expired before a match occurred. |

EFI_OUT_OF_RESOURCES |

The request could not be completed due to a lack of resources. |

14.2.4. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Mem.Read()

14.2.5. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Mem.Write()

Summary

Enables a PCI driver to access PCI controller registers in the PCI root bridge memory space.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_IO_MEM) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 Address,

IN UINTN Count,

IN OUT VOID *Buffer

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in PCI Root Bridge I/O Protocol .

- Width

Signifies the width of the memory operation. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH see Related Definitions in the section PCI Root Bridge I/O Protocol .

- Address

The base address of the memory operation. The caller is responsible for aligning the Address if required.

- Count

The number of memory operations to perform. Bytes moved is Width size * Count, starting at Address.

- Buffer

For read operations, the destination buffer to store the results. For write operations, the source buffer to write data from.

Description

The Mem.Read() , and Mem.Write() functions enable a driver to access PCI controller registers in the PCI root bridge memory space.

The memory operations are carried out exactly as requested. The caller is responsible for satisfying any alignment and memory width restrictions that a PCI Root Bridge on a platform might require. For example on some platforms, width requests of EfiPciWidthUint64 do not work.

If Width is EfiPciWidthUint8 , EfiPciWidthUint16 , EfiPciWidthUint32 , or EfiPciWidthUint64 , then both Address and Buffer are incremented for each of the Count operations performed.

If Width is EfiPciWidthFifoUint8 , EfiPciWidthFifoUint16 , EfiPciWidthFifoUint32 , or EfiPciWidthFifoUint64 , then only Buffer is incremented for each of the Count operations performed. The read or write operation is performed Count times on the same Address.

If Width is EfiPciWidthFillUint8 , EfiPciWidthFillUint16 , EfiPciWidthFillUint32 , or EfiPciWidthFillUint64 , then only Address is incremented for each of the Count operations performed. The read or write operation is performed Count times from the first element of Buffer.

All the PCI read transactions generated by this function are guaranteed to be completed before this function returns. All the PCI write transactions generated by this function will follow the write ordering and completion rules defined in the PCI Specification. However, if the memory-mapped I/O region being accessed by this function has the EFI_PCI_ATTRIBUTE_MEMORY_CACHED attribute set, then the transactions will follow the ordering rules defined by the processor architecture.

Status Codes Returned

EFI_SUCCESS |

The data was read from or written to the PCI root bridge. |

EFI_INVALID_PARAMETER |

Width is invalid for this PCI root bridge. |

EFI_INVALID_PARAMETER |

Buffer is NULL. |

EFI_OUT_OF_RESOURCES |

The request could not be completed due to a lack of resources. |

14.2.6. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Io.Read()

14.2.7. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Io.Write()

Summary

Enables a PCI driver to access PCI controller registers in the PCI root bridge I/O space.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_IO_MEM) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 Address,

IN UINTN Count,

IN OUT VOID *Buffer

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in PCI Root Bridge I/O Protocol .

- Width

Signifies the width of the memory operation. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH see Related Definitions in the section PCI Root Bridge I/O Protocol .

- Address

The base address of the I/O operation. The caller is responsible for aligning the Address if required.

- Count

The number of I/O operations to perform. Bytes moved is Width size * Count, starting at Address.

- Buffer

For read operations, the destination buffer to store the results. For write operations, the source buffer to write data from.

Description

The Io.Read() , and Io.Write() functions enable a driver to access PCI controller registers in the PCI root bridge I/O space.

The I/O operations are carried out exactly as requested. The caller is responsible for satisfying any alignment and I/O width restrictions that a PCI root bridge on a platform might require. For example on some platforms, width requests of EfiPciWidthUint64 do not work.

If Width is EfiPciWidthUint8 , EfiPciWidthUint16 , EfiPciWidthUint32 , or EfiPciWidthUint64 , then both Address and Buffer are incremented for each of the Count operations performed.

If Width is EfiPciWidthFifoUint8 , EfiPciWidthFifoUint16 , EfiPciWidthFifoUint32 , or EfiPciWidthFifoUint64 , then only Buffer is incremented for each of the Count operations performed. The read or write operation is performed Count times on the same Address.

If Width is EfiPciWidthFillUint8 , EfiPciWidthFillUint16 , EfiPciWidthFillUint32 , or EfiPciWidthFillUint64 , then only Address is incremented for each of the Count operations performed. The read or write operation is performed Count times from the first element of Buffer.

All the PCI transactions generated by this function are guaranteed to be completed before this function returns.

Status Codes Returned

EFI_SUCCESS |

The data was read from or written to the PCI root bridge. |

EFI_INVALID_PARAMETER |

Width is invalid for this PCI root bridge. |

EFI_INVALID_PARAMETER |

Buffer is NULL. |

EFI_OUT_OF_RESOURCES |

The request could not be completed due to a lack of resources. |

14.2.8. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Pci.Read()

14.2.9. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Pci.Write()

Summary

Enables a PCI driver to access PCI controller registers in a PCI root bridge’s configuration space.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_IO_MEM) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 Address,

IN UINTN Count,

IN OUT VOID *Buffer

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in PCI Root Bridge I/O Protocol .

- Width

Signifies the width of the memory operation. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH see Related Definitions in the section PCI Root Bridge I/O Protocol .

- Address

The address within the PCI configuration space for the PCI controller. See PCI Configuration Address for the format of Address.

- Count

The number of PCI configuration operations to perform. Bytes moved is Width size * Count, starting at Address.

- Buffer

For read operations, the destination buffer to store the results. For write operations, the source buffer to write data from.

Description

The Pci.Read() and Pci.Write() functions enable a driver to access PCI configuration registers for a PCI controller.

The PCI Configuration operations are carried out exactly as requested. The caller is responsible for any alignment and PCI configuration width issues that a PCI Root Bridge on a platform might require. For example on some platforms, width requests of EfiPciWidthUint64 do not work.

If Width is EfiPciWidthUint8 , EfiPciWidthUint16 , EfiPciWidthUint32 , or EfiPciWidthUint64 , then both Address and Buffer are incremented for each of the Count operations performed.

If Width is EfiPciWidthFifoUint8 , EfiPciWidthFifoUint16 , EfiPciWidthFifoUint32 , or EfiPciWidthFifoUint64 , then only Buffer is incremented for each of the Count operations performed. The read or write operation is performed Count times on the same Address.

If Width is EfiPciWidthFillUint8, EfiPciWidthFillUint16, EfiPciWidthFillUint32, or EfiPciWidthFillUint64, then only Address is incremented for each of the Count operations performed. The read or write operation is performed Count times from the first element of Buffer.

All the PCI transactions generated by this function are guaranteed to be completed before this function returns.

Mnemonic |

Byte Offset |

Byte Length |

Description |

Register |

0 |

1 |

The register number on the PCI Function. |

Function |

1 |

1 |

The PCI Function number on the PCI Device. |

Device |

2 |

1 |

The PCI Device number on the PCI Bus. |

Bus |

3 |

1 |

The PCI Bus number. |

ExtendedRegister |

4 |

4 |

The register number on the PCI Function. If this field is zero, then the Register field is used for the register number. If this field is nonzero, then the Register field is ignored, and the E xtendedRegister field is used for the register number. |

Status Codes Returned

EFI_SUCCESS |

The data was read from or written to the PCI root bridge. |

EFI_INVALID_PARAMETER |

Width is invalid for this PCI root bridge. |

EFI_INVALID_PARAMETER |

Buffer is NULL. |

EFI_OUT_OF_RESOURCES |

The request could not be completed due to a lack of resources. |

14.2.10. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.CopyMem()

Summary

Enables a PCI driver to copy one region of PCI root bridge memory space to another region of PCI root bridge memory space.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_COPY_MEM) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH Width,

IN UINT64 DestAddress,

IN UINT64 SrcAddress,

IN UINTN Count

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in PCI Root Bridge I/O Protocol .

- Width

Signifies the width of the memory operation. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_WIDTH see Related Definitions in the section PCI Root Bridge I/O Protocol .

- DestAddress

The destination address of the memory operation. The caller is responsible for aligning the DestAddress if required.

- SrcAddress

The source address of the memory operation. The caller is responsible for aligning the SrcAddress if required.

- Count

The number of memory operations to perform. Bytes moved is Width size * Count, starting at DestAddress and SrcAddress.

Description

The CopyMem() function enables a PCI driver to copy one region of PCI root bridge memory space to another region of PCI root bridge memory space. This is especially useful for video scroll operation on a memory mapped video buffer.

The memory operations are carried out exactly as requested. The caller is responsible for satisfying any alignment and memory width restrictions that a PCI root bridge on a platform might require. For example on some platforms, width requests of EfiPciWidthUint64 do not work.

If Width is EfiPciIoWidthUint8 , EfiPciIoWidthUint16 , EfiPciIoWidthUint32 , or EfiPciIoWidthUint64 , then Count read/write transactions are performed to move the contents of the SrcAddress buffer to the DestAddress buffer. The implementation must be reentrant, and it must handle overlapping SrcAddress and DestAddress buffers. This means that the implementation of CopyMem() must choose the correct direction of the copy operation based on the type of overlap that exists between the SrcAddress and DestAddress buffers. If either the SrcAddress buffer or the DestAddress buffer crosses the top of the processor’s address space, then the result of the copy operation is unpredictable.

The contents of the DestAddress buffer on exit from this service must match the contents of the SrcAddress buffer on entry to this service. Due to potential overlaps, the contents of the SrcAddress buffer may be modified by this service. The following rules can be used to guarantee the correct behavior:

If DestAddress > SrcAddress and DestAddress < ( SrcAddress + Width size * Count ), then the data should be copied from the SrcAddress buffer to the DestAddress buffer starting from the end of buffers and working toward the beginning of the buffers.

Otherwise, the data should be copied from the SrcAddress buffer to the DestAddress buffer starting from the beginning of the buffers and working toward the end of the buffers.

All the PCI transactions generated by this function are guaranteed to be completed before this function returns. All the PCI write transactions generated by this function will follow the write ordering and completion rules defined in the PCI Specification. However, if the memory-mapped I/O region being accessed by this function has the EFI_PCI_ATTRIBUTE_MEMORY_CACHED attribute set, then the transactions will follow the ordering rules defined by the processor architecture.

Status Codes Returned

EFI_SUCCESS |

The data was copied from one memory region to another memory region. |

EFI_INVALID_PARAMETER |

Width is invalid for this PCI root bridge. |

EFI_OUT_OF_RESOURCES |

The request could not be completed due to a lack of resources. |

14.2.11. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map()

Summary

Provides the PCI controller-specific addresses required to access system memory from a DMA bus master.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_MAP) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_OPERATION Operation,

IN VOID *HostAddress,

IN OUT UINTN *NumberOfBytes,

OUT EFI_PHYSICAL_ADDRESS *DeviceAddress,

OUT VOID **Mapping

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in PCI Root Bridge I/O Protocol .

- Operation

Indicates if the bus master is going to read or write to system memory. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_OPERATION defined in Section PCI Root Bridge I/O Protocol .

- HostAddress

The system memory address to map to the PCI controller.

- NumberOfBytes

On input the number of bytes to map. On output the number of bytes that were mapped.

- DeviceAddress

The resulting map address for the bus master PCI controller to use to access the system memory’s HostAddress. Type EFI_PHYSICAL_ADDRESS , defined in EFI_BOOT_SERVICES.AllocatePool(). This address cannot be used by the processor to access the contents of the buffer specified by HostAddress.

- Mapping

The value to pass to Unmap() when the bus master DMA operation is complete.

Description

The Map() function provides the PCI controller specific addresses needed to access system memory. This function is used to map system memory for PCI bus master DMA accesses.

All PCI bus master accesses must be performed through their mapped addresses and such mappings must be freed with EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Unmap() when complete. If the bus master access is a single read or single write data transfer, then EfiPciOperationBusMasterRead , EfiPciOperationBusMasterRead64 , EfiPciOperationBusMasterWrite , or EfiPciOperationBusMasterWrite64 is used and the range is unmapped to complete the operation. If performing an EfiPciOperationBusMasterRead or EfiPciOperationBusMasterRead64 operation, all the data must be present in system memory before Map() is performed. Similarly, if performing an EfiPciOperation-BusMasterWrite or EfiPciOperationBusMasterWrite64 the data cannot be properly accessed in system memory until Unmap() is performed.

Bus master operations that require both read and write access or require multiple host device interactions within the same mapped region must use EfiPciOperation-BusMasterCommonBuffer or EfiPciOperationBusMasterCommonBuffer64. However, only memory allocated via the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.AllocateBuffer() interface can be mapped for this type of operation.

In all mapping requests the resulting NumberOfBytes actually mapped may be less than the requested amount. In this case, the DMA operation will have to be broken up into smaller chunks. The Map() function will map as much of the DMA operation as it can at one time. The caller may have to loop on Map() and Unmap() in order to complete a large DMA transfer.

Status Codes Returned

EFI_SUCCESS |

The range was mapped for the returned NumberOfBytes. |

EFI_INVALID_PARAMETER |

Operation is invalid. |

EFI_INVALID_PARAMETER |

HostAddress is NULL. |

EFI_INVALID_PARAMETER |

NumberOfBytes is NULL. |

EFI_INVALID_PARAMETER |

DeviceAddress is NULL. |

EFI_INVALID_PARAMETER |

Mapping is NULL. |

EFI_UNSUPPORTED |

The HostAddress cannot be mapped as a common buffer. |

EFI_DEVICE_ERROR |

The system hardware could not map the requested address. |

EFI_OUT_OF_RESOURCES |

The request could not be completed due to a lack of resources. |

14.2.12. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Unmap()

Summary

Completes the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map() operation and releases any corresponding resources.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_UNMAP) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN VOID *Mapping

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL , defined in PCI Root Bridge I/O Protocol .

- Mapping

The mapping value returned from Map().

Description

The Unmap() function completes the Map() operation and releases any corresponding resources. If the operation was an EfiPciOperationBusMasterWrite or EfiPciOperationBusMasterWrite64 , the data is committed to the target system memory. Any resources used for the mapping are freed.

Status Codes Returned

EFI_SUCCESS |

The range was unmapped. |

EFI_INVALID_PARAMETER |

Mapping is not a value that was returned by Map(). |

EFI_DEVICE_ERROR |

The data was not committed to the target system memory. |

14.2.13. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.AllocateBuffer()

Summary

Allocates pages that are suitable for an EfiPciOperationBusMasterCommonBuffer or EfiPciOperationBusMasterCommonBuffer64 mapping.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_ALLOCATE_BUFFER) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN EFI_ALLOCATE_TYPE Type,

IN EFI_MEMORY_TYPE MemoryType,

IN UINTN Pages,

OUT VOID **HostAddress,

IN UINT64 Attributes

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL . Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in Section PCI Root Bridge I/O Protocol .

- Type

This parameter is not used and must be ignored.

- Memory

Type The type of memory to allocate, EfiBootServicesData or EfiRuntimeServicesData. Type EFI_MEMORY_TYPE is defined in EFI_BOOT_SERVICES.AllocatePages().

- Pages

The number of pages to allocate.

- HostAddress

A pointer to store the base system memory address of the allocated range.

- Attributes

The requested bit mask of attributes for the allocated range. Only the attributes EFI_PCI_ATTRIBUTE_MEMORY_WRITE_COMBINE , EFI_PCI_ATTRIBUTE_MEMORY_CACHED , and EFI_PCI_ATTRIBUTE_DUAL_ADDRESS_CYCLE may be used with this function. If any other bits are set, then EFI_UNSUPPORTED is returned. This function may choose to ignore this bit mask. The EFI_PCI_ATTRIBUTE_MEMORY_WRITE_COMBINE , and EFI_PCI_ATTRIBUTE_MEMORY_CACHED attributes provide a hint to the implementation that may improve the performance of the calling driver. The implementation may choose any default for the memory attributes including write combining, cached, both, or neither as long as the allocated buffer can be seen equally by both the processor and the PCI bus master.

Description

The AllocateBuffer() function allocates pages that are suitable for an EfiPciOperationBusMasterCommonBuffer or EfiPciOperationBusMasterCommonBuffer64 mapping. This means that the buffer allocated by this function must support simultaneous access by both the processor and a PCI Bus Master. The device address that the PCI Bus Master uses to access the buffer can be retrieved with a call to EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Map() .

If the EFI_PCI_ATTRIBUTE_DUAL_ADDRESS_CYCLE bit of Attributes is set, then when the buffer allocated by this function is mapped with a call to Map() , the device address that is returned by Map() must be within the 64-bit device address space of the PCI Bus Master.

If the EFI_PCI_ATTRIBUTE_DUAL_ADDRESS_CYCLE bit of Attributes is clear, then when the buffer allocated by this function is mapped with a call to Map() , the device address that is returned by Map() must be within the 32-bit device address space of the PCI Bus Master.

If the memory allocation specified by MemoryType and Pages cannot be satisfied, then EFI_OUT_OF_RESOURCES is returned.

Status Codes Returned

EFI_SUCCESS |

The requested memory pages were allocated. |

EFI_INVALID_PARAMETER |

MemoryType is invalid. |

EFI_INVALID_PARAMETER |

HostAddress is NULL. |

EFI_UNSUPPORTED |

Attributes is unsupported. The only legal attribute bits are

EFI_PCI_ATTRIBUTE_MEMORY_WRITE_COMBINE ,

EFI_PCI_ATTRIBUTE_MEMORY_CACHED , and

EFI_PCI_ATTRIBUTE_DUAL_ADDRESS_CYCLE.

|

EFI_OUT_OF_RESOURCES |

The memory pages could not be allocated. |

14.2.14. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.FreeBuffer()

Summary

Frees memory that was allocated with EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.AllocateBuffer().

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_FREE_BUFFER) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN UINTN Pages,

IN VOID *HostAddress

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in PCI Root Bridge I/O Protocol .

- Pages

The number of pages to free.

- HostAddress

The base system memory address of the allocated range.

Description

The FreeBuffer() function frees memory that was allocated with AllocateBuffer().

Status Codes Returned

EFI_SUCCESS |

The requested memory pages were freed. |

EFI_INVALID_PARAMETER |

The memory range specified by HostAddress and Pages was not allocated with AllocateBuffer(). |

14.2.15. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Flush()

Summary

Flushes all PCI posted write transactions from a PCI host bridge to system memory.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_FLUSH) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in Section PCI Root Bridge I/O Protocol .

Description

The Flush() function flushes any PCI posted write transactions from a PCI host bridge to system memory. Posted write transactions are generated by PCI bus masters when they perform write transactions to target addresses in system memory.

This function does not flush posted write transactions from any PCI bridges. A PCI controller specific action must be taken to guarantee that the posted write transactions have been flushed from the PCI controller and from all the PCI bridges into the PCI host bridge. This is typically done with a PCI read transaction from the PCI controller prior to calling Flush().

If the PCI controller specific action required to flush the PCI posted write transactions has been performed, and this function returns EFI_SUCCESS , then the PCI bus master’s view and the processor’s view of system memory are guaranteed to be coherent. If the PCI posted write transactions cannot be flushed from the PCI host bridge, then the PCI bus master and processor are not guaranteed to have a coherent view of system memory, and EFI_DEVICE_ERROR is returned.

Status Codes Returned

EFI_SUCCESS |

The PCI posted write transactions were flushed from the PCI host bridge to system memory. |

EFI_DEVICE_ERROR |

The PCI posted write transactions were not flushed from the PCI host bridge due to a hardware error. |

14.2.16. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.GetAttributes()

Summary

Gets the attributes that a PCI root bridge supports setting with EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.SetAttributes() , and the attributes that a PCI root bridge is currently using. Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_GET_ATTRIBUTES) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

OUT UINT64 *Supports OPTIONAL,

OUT UINT64 *Attributes OPTIONAL

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in Section PCI Root Bridge I/O Protocol .

- Supports

A pointer to the mask of attributes that this PCI root bridge supports setting with SetAttributes(). The available attributes are listed in See PCI Root Bridge I/O Protocol. This is an optional parameter that may be NULL.

- Attributes

A pointer to the mask of attributes that this PCI root bridge is currently using. The available attributes are listed in See PCI Root Bridge I/O Protocol. This is an optional parameter that may be NULL.

Description

The GetAttributes() function returns the mask of attributes that this PCI root bridge supports and the mask of attributes that the PCI root bridge is currently using. If Supports is not NULL , then Supports is set to the mask of attributes that the PCI root bridge supports. If Attributes is not NULL , then Attributes is set to the mask of attributes that the PCI root bridge is currently using. If both Supports and Attributes are NULL , then EFI_INVALID_PARAMETER is returned. Otherwise, EFI_SUCCESS is returned.

If a bit is set in Supports , then the PCI root bridge supports this attribute type, and a call can be made to SetAttributes() using that attribute type. If a bit is set in Attributes , then the PCI root bridge is currently using that attribute type. Since a PCI host bus may be composed of more than one PCI root bridge, different Attributes values may be returned by different PCI root bridges.

Status Codes Returned

EFI_SUCCESS |

If Supports is not NULL , then the attributes that the PCI root bridge supports is returned in Supports. If Attributes is not NULL , then the attributes that the PCI root bridge is currently using is returned in Attributes. |

EFI_INVALID_PARAMETER |

Both Supports and Attributes are NULL. |

14.2.17. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.SetAttributes()

Summary

Sets attributes for a resource range on a PCI root bridge.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_SET_ATTRIBUTES) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

IN UINT64 Attributes,

IN OUT UINT64 *ResourceBase OPTIONAL,

IN OUT UINT64 *ResourceLength OPTIONAL

);

Parameters

- This

A pointer to the See EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL. Type EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL is defined in See PCI Root Bridge I/O Protocol.

- Attributes

The mask of attributes to set. If the attribute bit MEMORY_WRITE_COMBINE, MEMORY_CACHED, or MEMORY_DISABLE is set, then the resource range is specified by ResourceBase and ResourceLength. If MEMORY_WRITE_COMBINE, MEMORY_CACHED, and MEMORY_DISABLE are not set, then ResourceBase and ResourceLength are ignored, and may be NULL. The available attributes are listed in See PCI Root Bridge I/O Protocol.

- ResourceBase

A pointer to the base address of the resource range to be modified by the attributes specified by Attributes. On return, ResourceBase will be set the actual base address of the resource range. Not all resources can be set to a byte boundary, so the actual base address may differ from the one passed in by the caller. This parameter is only used if the MEMORY_WRITE_COMBINE bit, the MEMORY_CACHED bit, or the MEMORY_DISABLE bit of Attributes is set. Otherwise, it is ignored, and may be NULL.

- ResourceLength

A pointer to the length of the resource range to be modified by the attributes specified by Attributes. On return, ResourceLength will be set the actual length of the resource range. Not all resources can be set to a byte boundary, so the actual length may differ from the one passed in by the caller. This parameter is only used if the MEMORY_WRITE_COMBINE bit, the MEMORY_CACHED bit, or the MEMORY_DISABLE bit of Attributes is set. Otherwise, it is ignored, and may be **NULL*.

Description

The SetAttributes() function sets the attributes specified in Attributes for the PCI root bridge on the resource range specified by ResourceBase and ResourceLength. Since the granularity of setting these attributes may vary from resource type to resource type, and from platform to platform, the actual resource range and the one passed in by the caller may differ. As a result, this function may set the attributes specified by Attributes on a larger resource range than the caller requested. The actual range is returned in ResourceBase and ResourceLength. The caller is responsible for verifying that the actual range for which the attributes were set is acceptable.

If the attributes are set on the PCI root bridge, then the actual resource range is returned in ResourceBase and ResourceLength , and EFI_SUCCESS is returned.

If the attributes specified by Attributes are not supported by the PCI root bridge, then EFI_UNSUPPORTED is returned. The set of supported attributes for a PCI root bridge can be found by calling EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.GetAttributes().

If either ResourceBase or ResourceLength are NULL , and a resource range is required for the attributes specified in Attributes , then EFI_INVALID_PARAMETER is returned.

If more than one resource range is required for the set of attributes specified by Attributes , then EFI_INVALID_PARAMETER is returned.

If there are not enough resources available to set the attributes, then EFI_OUT_OF_RESOURCES is returned.

Status Codes Returned

EFI_SUCCESS |

The set of attributes specified by Attributes for the resource range specified by ResourceBase and ResourceLength were set on the PCI root bridge, and the actual resource range is returned in ResuourceBase and ResourceLength. |

EFI_UNSUPPORTED |

A bit is set in Attributes that is not supported by the PCI Root Bridge. The supported attribute bits are reported by EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.GetAttributes() |

EFI_INVALID_PARAMETER |

More than one attribute bit is set in Attributes that requires a resource range. |

EFI_INVALID_PARAMETER |

A resource range is required, and ResourceBase is NULL. |

EFI_INVALID_PARAMETER |

A resource range is required, and ResourceLength is NULL. |

EFI_OUT_OF_RESOURCES |

There are not enough resources to set the attributes on the resource range specified by BaseAddress and Length. |

14.2.18. EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL.Configuration()

Summary

Retrieves the current resource settings of this PCI root bridge in the form of a set of ACPI resource descriptors.

Prototype

typedef

EFI_STATUS

(EFIAPI *EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL_CONFIGURATION) (

IN EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL *This,

OUT VOID **Resources

);

Parameters

- This

A pointer to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL, which is defined in PCI Root Bridge I/O Protocol.

- Resources

A pointer to the resource descriptors that describe the current configuration of this PCI root bridge. The storage for the resource descriptors is allocated by this function. The caller must treat the return buffer as read-only data, and the buffer must not be freed by the caller. See “Related Definitions” for the resource descriptors that may be used.

Related Definitions

There are only two resource descriptor types from the ACPI Specification that may be used to describe the current resources allocated to a PCI root bridge. These are the QWORD Address Space Descriptor, and the End Tag. The QWORD Address Space Descriptor can describe memory, I/O, and bus number ranges for dynamic or fixed resources. The configuration of a PCI root bridge is described in the Tables below with one or more QWORD Address Space Descriptors followed by an End Tag which contain these two descriptor types.

Please see the ACPI Specification for details on the field values. The definition of the Address Space Granularity field in the QWORD Address Space Descriptor differs from the ACPI Specification, and the definition in the table below is the one that must be used.

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x8A |

QWORD Address Space Descriptor |

0x01 |

0x02 |

0x2B |

Length of this descriptor in bytes not including the first two fields |

0x03 |

0x01 |

Resource Type

0 - Memory Range

1 - I/O Range

2 - Bus Number Range

|

|

0x04 |

0x01 |

General Flags |

|

0x05 |

0x01 |

Type Specific Flags |

|

0x06 |

0x08 |

Address Space Granularity. Used to differentiate between a 32-bit memory request and a 64-bit memory request. For a 32-bit memory request, this field should be set to 32. For a 64-bit memory request, this field should be set to 64. |

|

0x0E |

0x08 |

Address Range Minimum |

|

0x16 |

0x08 |

Address Range Maximum |

|

0x1E |

0x08 |

Address Translation Offset. Offset to apply to the Starting address to convert it to a PCI address. This value is zero unless the HostAddress and DeviceAddress for the root bridge are different. |

|

0x26 |

0x08 |

Address Length |

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x79 |

End Tag |

0x01 |

0x01 |

0x00 |

Checksum. If 0, then checksum is assumed to be valid. |

Description

The Configuration() function retrieves a set of resource descriptors that contains the current configuration of this PCI root bridge. If the current configuration can be retrieved, then it is returned in Resources and EFI_SUCCESS is returned. See “Related Definitions” below for the resource descriptor types that are supported by this function. If the current configuration cannot be retrieved, then EFI_UNSUPPORTED is returned.

Status Codes Returned

EFI_SUCCESS |

The current configuration of this PCI root bridge was returned in Resources. |

EFI_UNSUPPORTED |

The current configuration of this PCI root bridge could not be retrieved. |

14.2.19. PCI Root Bridge Device Paths

See EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL must be installed on a handle for its services to be available to drivers. In addition to the EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL , an EFI Device Path Protocol must also be installed on the same handle.

Typically, an ACPI Device Path Node is used to describe a PCI Root Bridge. Depending on the bus hierarchy in the system, additional device path nodes may precede this ACPI Device Path Node. A desktop system will typically contain only one PCI Root Bridge, so there would be one handle with a EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL and an EFI_DEVICE_PATH_PROTOCOL A server system may contain multiple PCI Root Bridges, so it would contain a handle for each PCI Root Bridge present, and on each of those handles would be an EFI_PCI_ROOT_BRIDGE_IO_PROTOCOL and an EFI_DEVICE_PATH_PROTOCOL. In all cases, the contents of the ACPI Device Path Nodes for PCI Root Bridges must match the information present in the ACPI tables for that system.

Table below: PCI Root Bridge Device Path for a Desktop System shows an example device path for a PCI Root Bridge in a desktop system. Today, a desktop system typically contains one PCI Root Bridge. This device path consists of an ACPI Device Path Node, and a Device Path End Structure. The _HID and _UID must match the ACPI table description of the PCI Root Bridge. For a system with only one PCI Root Bridge, the _UID value is usually 0x0000. The shorthand notation for this device path is ACPI(PNP0A03,0).

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x02 |

Generic Device Path Header - Type ACPI Device Path |

0x01 |

0x01 |

0x01 |

Sub type - ACPI Device Path |

0x02 |

0x02 |

0x0C |

Length - 0x0C bytes |

0x04 |

0x04 |

0x41D0, 0x0A03 |

_HID PNP0A03 - 0x41D0 represents the compressed string ‘PNP’ and is encoded in the low order bytes. The compression method is described in the ACPI Specification. |

0x08 |

0x04 |

0x0000 |

_UID |

0x0C |

0x01 |

0x7F |

Generic Device Path Header - Type End of Hardware Device Path |

0x0D |

0x01 |

0xFF |

Sub type - End of Entire Device Path |

0x0E |

0x02 |

0x04 |

Length - 0x04 bytes |

In the Tables belows, PCI Root Bridge Device Path for Bridge #0 in a Server System through PCI Root Bridge Device Path for Bridge #3 in a Server System show example device paths for the PCI Root Bridges in a server system with four PCI Root Bridges. Each of these device paths consists of an ACPI Device Path Node, and a Device Path End Structure. The _HID and _UID must match the ACPI table description of the PCI Root Bridges. The only difference between each of these device paths is the _UID field. The shorthand notation for these four device paths is ACPI(PNP0A03,0) , ACPI(PNP0A03,1) , ACPI(PNP0A03,2) , and ACPI(PNP0A03,3).

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x02 |

Generic Device Path Header - Type ACPI Device Path |

0x01 |

0x01 |

0x01 |

Sub type - ACPI Device Path |

0x02 |

0x02 |

0x0C |

Length - 0x0C bytes |

0x04 |

0x04 |

0x41D0, 0x0A03 |

_HID PNP0A03 - 0x41D0 represents the compressed string ‘PNP’ and is encoded in the low order bytes. The compression method is described in the ACPI Specification. |

0x08 |

0x04 |

0x0000 |

_UID |

0x0C |

0x01 |

0x7F |

Generic Device Path Header - Type End of Hardware Device Path |

0x0D |

0x01 |

0xFF |

Sub type - End of Entire Device Path |

0x0E |

0x02 |

0x04 |

Length - 0x04 bytes |

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x02 |

Generic Device Path Header - Type ACPI Device Path |

0x01 |

0x01 |

0x01 |

Sub type - ACPI Device Path |

0x02 |

0x02 |

0x0C |

Length - 0x0C bytes |

0x04 |

0x04 |

0x41D0, 0x0A03 |

_HID PNP0A03 - 0x41D0 represents the compressed string ‘PNP’ and is encoded in the low order bytes. The compression method is described in the ACPI Specification. |

0x08 |

0x04 |

0x0001 |

_UID |

0x0C |

0x01 |

0x7F |

Generic Device Path Header - Type End of Hardware Device Path |

0x0D |

0x01 |

0xFF |

Sub type - End of Entire Device Path |

0x0E |

0x02 |

0x04 |

Length - 0x04 bytes |

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x02 |

Generic Device Path Header - Type ACPI Device Path |

0x01 |

0x01 |

0x01 |

Sub type - ACPI Device Path |

0x02 |

0x02 |

0x0C |

Length - 0x0C bytes |

0x04 |

0x04 |

0x41D0, 0x0A03 |

_HID PNP0A03 - 0x41D0 represents the compressed string ‘PNP’ and is encoded in the low order bytes. The compression method is described in the ACPI Specification. |

0x08 |

0x04 |

0x0002 |

_UID |

0x0C |

0x01 |

0x7F |

Generic Device Path Header - Type End of Hardware Device Path |

0x0D |

0x01 |

0xF |

Sub type - End of Entire Device Path |

0x0E |

0x02 |

0x04 |

Length - 0x04 bytes |

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x02 |

Generic Device Path Header - Type ACPI Device Path |

0x01 |

0x01 |

0x01 |

Sub type - ACPI Device Path |

0x02 |

0x02 |

0x0C |

Length - 0x0C bytes |

0x04 |

0x04 |

0x41D0, 0x0A03 |

_HID PNP0A03 - 0x41D0 represents the compressed string ‘PNP’ and is encoded in the low order bytes. The compression method is described in the ACPI Specification. |

0x08 |

0x04 |

0x0003 |

_UID |

0x0C |

0x01 |

0x7F |

Generic Device Path Header - Type End of Hardware Device Path |

0x0D |

0x01 |

0xFF |

Sub type - End of Entire Device Path |

0x0E |

0x02 |

0x04 |

Length - 0x04 bytes |

The Table below, PCI Root Bridge Device Path Using Expanded ACPI Device Path , shows an example device path for a PCI Root Bridge using an Expanded ACPI Device Path. This device path consists of an Expanded ACPI Device Path Node, and a Device Path End Structure. The _UID and _CID fields must match the ACPI table description of the PCI Root Bridge. For a system with only one PCI Root Bridge, the _UID value is usually 0x0000. The shorthand notation for this device path is ACPI(12345678,0,PNP0A03).

Byte Offset |

Byte Length |

Data |

Description |

0x00 |

0x01 |

0x02 |

Generic Device Path Header - Type ACPI Device Path |

0x01 |

0x01 |

0x02 |

Sub type - Expanded ACPI Device Path |

0x02 |

0x02 |

0x10 |

Length - 0x10 bytes |

0x04 |

0x04 |

0x1234, 0x5678 |

_HID-device specific |

0x08 |

0x04 |

0x0000 |

_UID |

0x0C |

0x04 |

0x41D0, 0x0A03 |

_CID PNP0A03 - 0x41D0 represents the compressed string ‘PNP’ and is encoded in the low order bytes. The compression method is described in the ACPI Specification. |

0x10 |

0x01 |

0x7F |

Generic Device Path Header - Type End of Hardware Device Path |

0x11 |

0x01 |

0xFF |

Sub type - End of Entire Device Path |

0x12 |

0x02 |

0x04 |

Length - 0x04 bytes |

14.3. PCI Driver Model

PCI Driver Model and EFI PCI I/O Protocol describe the PCI Driver Model. This includes the behavior of PCI Bus Drivers, the behavior of a PCI Device Drivers, and a detailed description of the PCI I/O Protocol. The PCI Bus Driver manages PCI buses present in a system, and PCI Device Drivers manage PCI controllers present on PCI buses. The PCI Device Drivers produce an I/O abstraction that can be used to boot an EFI compliant operating system.

This document provides enough material to implement a PCI Bus Driver, and the tools required to design and implement a PCI Device Drivers. It does not provide any information on specific PCI devices.

The material contained in this section is designed to extend this specification and the UEFI Driver Model in a way that supports PCI device drivers and PCI bus drivers. These extensions are provided in the form of PCI-specific protocols. This section provides the information required to implement a PCI Bus Driver in system firmware. The section also contains the information required by driver writers to design and implement PCI Device Drivers that a platform may need to boot a UEFI-compliant OS.

The PCI Driver Model described here is intended to be a foundation on which a PCI Bus Driver and a wide variety of PCI Device Drivers can be created.

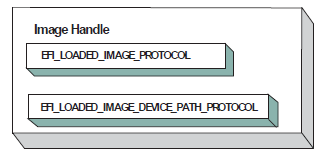

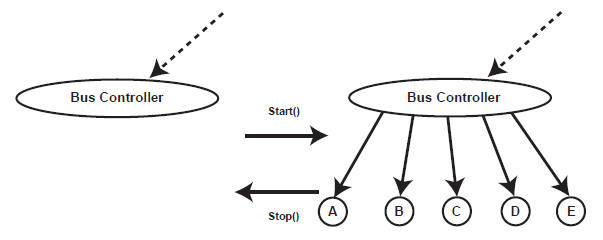

14.3.1. PCI Driver Initialization

There are very few differences between a PCI Bus Driver and PCI Device Driver in the entry point of the driver. The file for a driver image must be loaded from some type of media. This could include ROM, FLASH, hard drives, floppy drives, CD-ROM, or even a network connection. Once a driver image has been found, it can be loaded into system memory with the Boot Service: EFI_BOOT_SERVICES.LoadImage(). LoadImage() loads a PE/COFF formatted image into system memory. A handle is created for the driver, and a Loaded Image Protocol instance is placed on that handle. A handle that contains a Loaded Image Protocol instance is called an Image Handle. At this point, the driver has not been started. It is just sitting in memory waiting to be started. The figure below shows the state of an image handle for a driver after LoadImage() has been called.

Fig. 14.7 Image Handle

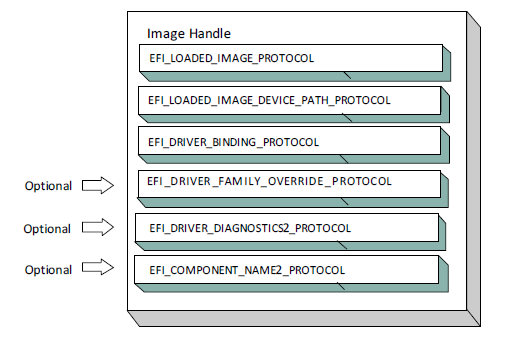

After a driver has been loaded with the Boot Service EFI_BOOT_SERVICES.LoadImage(), it must be started with the Boot Service EFI_BOOT_SERVICES.StartImage(). This is true of all types of applications and drivers that can be loaded and started on an UEFI compliant system. The entry point for a driver that follows the UEFI Driver Model must follow some strict rules. First, it is not allowed to touch any hardware. Instead, it is only allowed to install protocol instances onto its own Image Handle. A driver that follows the UEFI Driver Model is required to install an instance of the Driver Binding Protocol onto its own Image Handle. It may optionally install the Driver Diagnostics Protocol or the Component Name Protocol. In addition, if a driver wishes to be unloadable it may optionally update the Loaded Image Protocol to provide its own Unload() EFI_LOADED_IMAGE_PROTOCOL.Unload() function. Finally, if a driver needs to perform any special operations when the Boot Service EFI_BOOT_SERVICES is called ( Services — Boot Services ), the driver may optionally create an event with a notification function that is triggered when the Boot Service ExitBootServices() is called. An Image Handle that contains a Driver Binding Protocol instance is known as a Driver Image Handle. The Figure below, PCI Driver Image Handle, shows a possible configuration for the Image Handle from figure: Image Handle after the Boot Service StartImage() has been called.

Fig. 14.8 PCI Driver Image Handle

14.3.2. Driver Diagnostics Protocol

If a PCI Bus Driver or a PCI Device Driver requires diagnostics, then an EFI_DRIVER_DIAGNOSTICS2_PROTOCOL must be installed on the image handle in the entry point for the driver. This protocol contains functions to perform diagnostics on a controller. The EFI_DRIVER_DIAGNOSTICS2_PROTOCOL is not allowed to interact with the user. Instead, it must return status information through a bffer. The functions of this protocol will be invoked by a platform management utility.

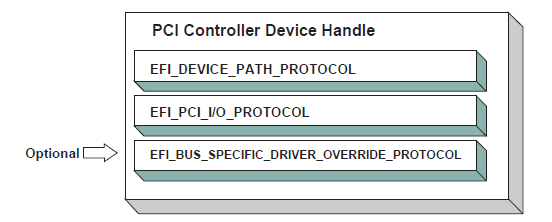

14.3.3. Component Name Protocol