# Platform Initialization (PI) Specification

# Volume 1: Pre-EFI Initialization Core Interface

Version 1.7 January 2019

The material contained herein is not a license, either expressly or impliedly, to any intellectual property owned or controlled by any of the authors or developers of this material or to any contribution thereto. The material contained herein is provided on an "AS IS" basis and, to the maximum extent permitted by applicable law, this information is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses and of lack of negligence, all with regard to this material and any contribution thereto. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." The Unified EFI Forum, Inc. reserves any features or instructions so marked for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. ALSO, THERE IS NO WARRANTY OR CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THE SPECIFICATION AND ANY CONTRIBUTION THERETO.

IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR ANY CONTRIBUTION THERETO BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT RELATING TO THIS DOCUMENT, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Copyright © 2018, Unified Extensible Firmware Interface (UEFI) Forum, Inc. All Rights Reserved. The UEFI Forum is the owner of all rights and title in and to this work, including all copyright rights that may exist, and all rights to use and reproduce this work. Further to such rights, permission is hereby granted to any person implementing this specification to maintain an electronic version of this work accessible by its internal personnel, and to print a copy of this specification in hard copy form, in whole or in part, in each case solely for use by that person in connection with the implementation of this Specification, provided no modification is made to the Specification.

# **Revision History**

| Revision     | Mantis ID / Description                                                                                      | Date             |

|--------------|--------------------------------------------------------------------------------------------------------------|------------------|

| 1.7          | 1848 PEI Core PEIM Migration Support Change                                                                  | January          |

|              | 1856 SecCore/PeiCore BFV Requirement Change                                                                  | 2019             |

|              | 1860 MM MP Protocol issues                                                                                   |                  |

|              | 1885 Add extended data for<br>EFI_SW_DXE_BS_EC_BOOT_OPTION_LOAD_ERROR                                        |                  |

|              | 1889 New Status Codes                                                                                        |                  |

|              | 1891 PEI delayed dispatch                                                                                    |                  |

|              | 1892 new pi spec revision                                                                                    |                  |

|              | 1955 set (*Attributes) when EFI_PEI_GET_VARIABLE2 returns<br>EFI_BUFFER_TOO_SMALL and Attributes is non-NULL |                  |

|              | 1967 New architectural PPI for PI PEI Core FV Location                                                       |                  |

|              | 1969 Incompatible Pci Ignore Option Rom                                                                      |                  |

| 1.6 Errata A | 1828 Add decorator 'OPTIONAL' for Attributes parameter of<br>EFI_PEI_GET_VARIABLE2.                          | December<br>2018 |

|              | 1849 Issues in PI Spec Vol. 5 Ch. 18                                                                         |                  |

|              | 1857 Specifies how notifications are passed from SEC to PEI.                                                 |                  |

|              | 1884 Variadic API issue in S3 save API                                                                       |                  |

|              | 1907 Clarification of the EFI_MM_COMMUNICATION_PROTOCOL                                                      |                  |

|              | 1940 Clarify EFI_MM_CONFIGURATION_PROTOCOL_GUID                                                              |                  |

| 1.6          | 1567 Layered SPI bus                                                                                         | April 2017       |

|              | 1648 PI Binding for RISC-V                                                                                   |                  |

|              | 1746 Add an FV Extended Header entry that contains the used size of the FV                                   |                  |

|              | 1763 MM Handler state notification protocol                                                                  |                  |

|              | 1764 Add additional alignment                                                                                |                  |

|              | 1768 Update the PI Spec to 1.6                                                                               |                  |

|              | 1777 Update Revision History                                                                                 |                  |

|              | 1778 Update front matter                                                                                     |                  |

| 1.5 Errata A | 1587 pre permanent memory page allocation                                                                    | April 2017       |

|              | 1665 Incorrect status code for an AP calling<br>EFI_MP_SERVICES_PROTOCOL.SwitchBSP()                         |                  |

|              | 1734 Outdated EFI spec reference in Save State Write                                                         |                  |

|              | 1735 Several copy & paste errors in Save State Write                                                         |                  |

|              | 1747 Clarify that MM_ACCESS_PROTOCOL should cover all MMRAM region used by the platform                      |                  |

| Revision     | Mantis ID / Description                                                               | Date    |

|--------------|---------------------------------------------------------------------------------------|---------|

| 1.5          | 1315 SMM Environment to Support Newer Architecture/Platform Designs                   | 4/26/16 |

|              | 1317 additional I2C PPI's (vol5)                                                      |         |

|              | 1321 ARM Extensions to Volume 4                                                       |         |

|              | 1330 Add PPI to allow SEC pass HOBs into PEI                                          |         |

|              | 1336 Provide For Pre-DXE Initialization Of The SM Foundation                          |         |

|              | 1369 Handling PEI PPI descriptor notifications from SEC                               |         |

|              | 1387 Variable services errors not consistent                                          |         |

|              | 1390 SM stand-alone infrastructure                                                    |         |

|              | 1396 Update SEC HOB Capabilities of 1330 with additional guidance                     |         |

|              | 1413 Communicate protocol enhancements                                                |         |

|              | 1506 New MP protocol                                                                  |         |

|              | 1513 Need a way to propagate PEI-phase FV verification status to DXE                  |         |

|              | 1563 Update MM PPIs to match existing implementations                                 |         |

|              | 1566 Pl.next - update the specification revisions                                     |         |

|              | 1568 Add SD/MMC GUID to DiskInfo protocol                                             |         |

|              | 1592 Add EFI_FV_FILETYPE_SMM_CORE_STANDALONE file type                                |         |

|              | 1593 coalesce language enhancements                                                   |         |

|              | 1594 Pei GetVaiable M1387 issue                                                       |         |

|              | 1595 M1568 Disk Info issue                                                            |         |

|              | • 1596 M1489 GCD issue                                                                |         |

|              | 1603 Minor erratas in Vol4 PI 1.5 draft related to ECR 0001506                        |         |

|              | 1607 Update MM guid def'n to match edkll impl                                         |         |

|              | 1626 Add new Status Code for BDS Attempting UEFI BootOrder entries                    |         |

|              | 1628 Minor feedback for PI 1.5 Vol 4 SMM Draft                                        |         |

|              | 1666 Graphics Device Info Hob                                                         |         |

| I.4 Errata A | 1574 Fix artificial limitation in the PCD.SetSku support                              | 3/15/16 |

|              | 1565 Update status code to include AArch64 exception error codes                      |         |

|              | 1564 SMM Software Dispatch Protocol Errata                                            |         |

|              | 1562 Errata to remove statement from DXE vol about PEI dispatch<br>behavior           |         |

|              | 1561 Errata to provide Equivalent of DXE-CIS Mantis 247 for the PEI-CIS               |         |

|              | 1532 Allow S3 Resume without having installed permanent memory (via InstallPeiMemory) |         |

|              | 1530 errata on dxe report status code                                                 |         |

|              | 1529 address space granularity errata                                                 |         |

|              | 1525 PEI Services Table Retrieval for AArch64                                         |         |

|              | 1515 EFI_PEIM_NOTIFY_ENTRY_POINT return values are undefined                          |         |

|              | 1497 Fixing language in SMMStartupThisAP                                              |         |

|              | 1489 GCD Conflict errata                                                              |         |

|              | 1485 Minor Errata in SMM Vo2 description of SMMStartupThisAP                          |         |

|              | 1397 PEI 1.4 specification revision errata                                            |         |

|              | 1394 Errata to Relax requirements on CPU rendez in SEC                                |         |

|              | 1351 EndOfDxe and SmmReadyToLock                                                      |         |

|              | 1322 Minor Updates to handle Asynchronous CPU Entry Into SMM                          |         |

| Revision     | Mantis ID / Description                                                                      | Date    |

|--------------|----------------------------------------------------------------------------------------------|---------|

| 1.4          | 1210 Adding persistence attribute to GCD                                                     | 2/20/15 |

|              | 1235 PI.Next Feature - no execute support                                                    |         |

|              | 1236 PI.Next feature - Graphics PPI                                                          |         |

|              | 1237 Pl.Next feature - add reset2 PPI                                                        |         |

|              | 1239 PI.Next feature - Disk Info Guid UFS                                                    |         |

|              | 1240 PI.Next feature - Recovery Block IO PPI - UFS                                           |         |

|              | 1259 PI.Next feature - MP PPI                                                                |         |

|              | 1273 Pl.Next feature - capsule PPI                                                           |         |

|              | 1274 Recovery Block I/O PPI Update                                                           |         |

|              | 1275 GetMemoryMap Update                                                                     |         |

|              | 1277 PI1.next feature - multiple CPU health info                                             |         |

|              | 1278 PI1.next - Memory relative reliability definition                                       |         |

|              | 1305 PI1.next - specification number encoding                                                |         |

|              | 1331 Remove left-over Boot Firmware Volume references in the SEC<br>Platform Information PPI |         |

|              | 1366 PI 1.4 draft - M1277 issue BIST / CPU. So health record needs to be indexed / CPU.      |         |

| 1.3 Errata A | 1041 typo in HOB Overview                                                                    | 2/19/15 |

|              | 1067 PI1.3 Errata for SetBootMode                                                            |         |

|              | 1068 Updates to PEI Service table/M1006                                                      |         |

|              | 1069 SIO Errata - pnp end node definition                                                    |         |

|              | 1070 Typo in SIO chapter                                                                     |         |

|              | 1072 Errata – SMM register protocol notify clarification/errata                              |         |

|              | 1093 Extended File Size Errata                                                               |         |

|              | 1095 typos/errata                                                                            |         |

|              | 1097 PI SMM GPI Errata                                                                       |         |

|              | 1098 Errata on I2C IO status code                                                            |         |

|              | 1099 I2C Protocol stop behavior errata                                                       |         |

|              | 1104 ACPI System Description Table Protocol Errata                                           |         |

|              | 1105 ACPI errata - supported table revision                                                  |         |

|              | 1177 PI errata - make CPU IO optional                                                        |         |

|              | 1178 errata - allow PEI to report an additional memory type                                  |         |

|              | 1283 Errata - clarify sequencing of events                                                   |         |

| 1.3          | 945 Integrated Circuit (I2C) Bus Protocol                                                    | 3/29/13 |

|              | 998 PI Status Code additions                                                                 |         |

|              | 999 PCI enumeration complete GUID                                                            |         |

|              | 1005 NVMe Disk Info guid                                                                     |         |

|              | 1006 Security Ppi Fixes                                                                      |         |

|              | 1025 PI table revisions                                                                      |         |

| Revision       | Mantis ID / Description                                                       | Date     |

|----------------|-------------------------------------------------------------------------------|----------|

| 1.2.1 Errata A | 922 Add a "Boot with Manufacturing" boot mode setting                         | 10/26/12 |

|                | 925 Errata on signed FV/Files                                                 |          |

|                | 931 DXE Volume 2 - Clarify memory map construction from the GCD               |          |

|                | 936 Clarify memory usage in PEI on S3                                         |          |

|                | 937SMM report protocol notify issue errata                                    |          |

|                | 951 Root Handler Processing by SmiManage                                      |          |

|                | • 958                                                                         |          |

|                | 969Vol 1 errata: TE Header parameters                                         |          |

| 1.2.1 Errata A | 922 Add a "Boot with Manufacturing" boot mode setting                         | 10/26/12 |

|                | 925 Errata on signed FV/Files                                                 |          |

|                | 931 DXE Volume 2 - Clarify memory map construction from the GCD               |          |

|                | 936 Clarify memory usage in PEI on S3                                         |          |

|                | 937 SMM report protocol notify issue errata                                   |          |

|                | 951 Root Handler Processing by SmiManage                                      |          |

|                | 958 Omissions in PI1.2.1 integration for M816 and M894                        |          |

|                | 969Vol 1 errata: TE Header parameters                                         |          |

| 1.2.1          | 527 PI Volume 2 DXE Security Architecture Protocol (SAP) clarification        | 05/02/12 |

|                | 562 Add SetMemoryCapabilities to GCD interface                                |          |

|                | 719 End of DXE event                                                          |          |

|                | 731 Volume 4 SMM - clarify the meaning of NumberOfCpus                        |          |

|                | 737 Remove SMM Communication ACPI Table definition .                          |          |

|                | 753 SIO PEI and UEFI-Driver Model Architecture                                |          |

|                | 769 Signed PI sections                                                        |          |

|                | 813 Add a new EFI_GET_PCD_INFO_PROTOCOL and<br>EFI_GET_PCD_INFO_PPI instance. |          |

|                | 818 New SAP2 return code                                                      |          |

|                | 822 Method to disable Temporary RAM when Temp RAM Migration is not required   |          |

|                | 833 Method to Reserve Interrupt and Exception Vectors                         |          |

|                | 839 Add support for weakly aligned FVs                                        |          |

|                | 892 EFI_PCI_ENUMERATION_COMPLETE_GUID Protocol                                |          |

|                | 894 SAP2 Update                                                               |          |

|                | 895 Status Code Data Structures Errata                                        |          |

|                | 902 Errata on signed firmware volume/file                                     |          |

|                | 903 SmiManage Update                                                          |          |

|                | 906 Volume 3 errata - Freeform type                                           |          |

|                | 916 Service table revisions                                                   |          |

| Revision     | Mantis ID / Description                                                             | Date     |

|--------------|-------------------------------------------------------------------------------------|----------|

| I.2 Errata C | 550 Naming conflicts w/ PI SMM                                                      | 10/27/11 |

|              | 571 duplicate definition of EFI_AP_PROCEDURE in DXE MP (volume2) and SMM (volume 4) |          |

|              | 654 UEFI PI specific handle for SMBIOS is now available                             |          |

|              | 688 Status Code errata                                                              |          |

|              | 690 Clarify agent in IDE Controller chapter                                         |          |

|              | 691 SMM a priori file and SOR support                                               |          |

|              | 692 Clarify the SMM SW Register API                                                 |          |

|              | 694 PEI Temp RAM PPI ambiguity                                                      |          |

|              | 703 End of PEI phase PPI publication for the S3 boot mode case                      |          |

|              | 706 GetPeiServicesTablePointer () changes for the ARM architecture                  |          |

|              | 714 PI Service Table Versions                                                       |          |

|              | 717 PI Extended File Size Errata                                                    |          |

|              | 718 PI Extended Header cleanup / Errata                                             |          |

|              | 730 typo in EFI_SMM_CPU_PROTOCOL.ReadSaveState() return code                        |          |

|              | 737 Remove SMM Communication ACPI Table definition .                                |          |

|              | 738 Errata to Volume 2 of the PI1.2 specification                                   |          |

|              | 739 Errata for PI SMM Volume 4 Control protocol                                     |          |

|              | 742 Errata for SMBUS chapter in Volume 5                                            |          |

|              | 743 Errata - PCD_PPI declaration                                                    |          |

|              | 745 Errata – PI Firmware Section declarations                                       |          |

|              | 746 Errata - PI status code                                                         |          |

|              | 747 Errata - Text for deprecated HOB                                                |          |

|              | 752 Binary Prefix change                                                            |          |

|              | 753 SIO PEI and UEFI-Driver Model Architecture                                      |          |

|              | 764 PI Volume 4 SMM naming errata                                                   |          |

|              | 775 errata/typo in EFI_STATUS_CODE_EXCEP_SYSTEM_CONTEXT,<br>Volume 3                |          |

|              | 781 S3 Save State Protocol Errata                                                   |          |

|              | 782 Format Insert(), Compare() and Label() as for Write()                           |          |

|              | 783 TemporaryRamMigration Errata                                                    |          |

|              | 784 Typos in status code definitions                                                |          |

|              | 787 S3 Save State Protocol Errata 2                                                 |          |

|              | 810 Set Memory Attributes return code clarification                                 |          |

|              | 811 SMBIOS API Clarification                                                        |          |

|              | 814 PI SMBIOS Errata                                                                |          |

|              | 821Location conflict for<br>EFI_RESOURCE_ATTRIBUTE_xxx_PROTECTABLE #defines         |          |

|              | 823 Clarify max length of SMBIOS Strings in SMBIOS Protocol                         |          |

|              | 824 EFI_SMM_SW_DISPATCH2_PROTOCOL.Register() Errata                                 |          |

|              | 837 ARM Vector table can not support arbitrary 32-bit address                       |          |

|              | 838 Vol 3 EFI_FVB2_ALIGNMNET_512K should be<br>EFI_FVB2_ALIGNMENT_512K              |          |

|              | 840 Vol 3 Table 5 Supported FFS Alignments contains values not supported by FFS     |          |

|              | 844 correct references to Platform Initialization Hand-Off Block<br>Specification   |          |

| Revision     | Mantis ID / Description                                                                                                        | Date     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2 errata B | 628 ACPI SDT protocol errata                                                                                                   | 5/27/10  |

|              | 629 Typos in PCD GetSize()                                                                                                     |          |

|              | 630EFI_SMM_PCI_ROOT_BRIDGE_IO_PROTOCOL service clarification                                                                   |          |

|              | 631 System Management System Table (SMST) MP-related field clarification                                                       |          |

| 1.2 errata A | 363 PI volume 1 errata                                                                                                         | 2/24/10  |

|              | 365 UEFI Capsule HOB                                                                                                           |          |

|              | 381 PI1.1 Errata on EFI_SMM_SAVE_STATE_IO_INFO                                                                                 |          |

|              | 482 One other naming inconsistency in the PCD PPI declaration                                                                  |          |

|              | 483 PCD Protocol / PPI function name synchronization                                                                           |          |

|              | 496 Boot mode description                                                                                                      |          |

|              | 497 Status Code additions                                                                                                      |          |

|              | 548 Boot firmware volume clarification                                                                                         |          |

|              | 551 Name conflicts w/ Legacy region                                                                                            |          |

|              | 552 MP services                                                                                                                |          |

|              | 553 Update text to PEI                                                                                                         |          |

|              | 554 update return code from PEI AllocatePages                                                                                  |          |

|              | 555 Inconsistency in the S3 protocol                                                                                           |          |

|              | 561 Minor update to PCD->SetPointer                                                                                            |          |

|              | 565 CANCEL_CALL_BACK should be CANCEL_CALLBACK                                                                                 |          |

|              | 569 Recovery: EFI_PEI_GET_NUMBER_BLOCK_DEVICES decl has<br>EFI_STATUS w/o return code & errror on stage 3 recovery description |          |

|              | 571 duplicate definition of EFI_AP_PROCEDURE in DXE MP (volume2) and SMM (volume 4)                                            |          |

|              | 581 EFI_HOB_TYPE_LOAD_PEIM ambiguity                                                                                           |          |

|              | 591ACPI Protocol Name collision                                                                                                |          |

|              | 592 More SMM name conflicts                                                                                                    |          |

|              | 593 A couple of ISA I/O clarifications                                                                                         |          |

|              | 594 ATA/ATAPI clarification                                                                                                    |          |

|              | 595 SMM driver entry point clarification                                                                                       |          |

|              | 596 Clarify ESAL return codes                                                                                                  |          |

|              | 602 SEC->PEI hand-off update                                                                                                   |          |

|              | 604 EFI_NOT_SUPPORTED versus EFI_UNSUPPORTED                                                                                   |          |

| 1.2          | 407 Comment: additional change to LMA Pseudo-Register                                                                          | 05/13/09 |

|              | 441 Comment: PI Volume 3, Incorrect Struct Declaration (esp PCD_PPI)                                                           |          |

|              | 455 Comment: Errata - Clarification of InstallPeiMemory()                                                                      |          |

|              | 465 Comment: Errata on PMI interface                                                                                           |          |

|              | 466 Comment: Vol 4 EXTENDED_SAL_PROC definition                                                                                |          |

|              | 467 Comments: PI1.1 errata                                                                                                     |          |

|              | 480 Comment: FIX to PCD_PROTOCOL and PCD_PPI                                                                                   |          |

| Revision | Mantis ID / Description                                           | Date     |

|----------|-------------------------------------------------------------------|----------|

| 1.2      | 401 SMM Volume 4 issue                                            | 02/23/09 |

|          | 402 SMM PI spec issue w.r.t. CRC                                  |          |

|          | 407 Add LMA Pseudo-Register to SMM Save State Protocol            |          |

|          | 409 PCD_PROTOCOL Errata                                           |          |

|          | 411 Draft Errata, Volume 5, Section 8                             |          |

|          | 412 Comment: PEI_S3_RESUME_PPI should be<br>EFI_PEI_S3_RESUME_PPI |          |

|          | 414 Draft Chapter 7 Comments                                      |          |

|          | 415 Comment: Report Status Code Routers                           |          |

|          | 416 EFI_CPU_IO_PROTOCOL2 Name should be<br>EFI_CPU_IO2_PROTOCOL   |          |

|          | 417 Volume 5, Chapter 4 & 5 order is reversed                     |          |

|          | 423 Comment: Section 15.2.1 Formatting Issues vol5                |          |

|          | 424 Comments: Volume 5, Appendix A.1 formatting issues            |          |

|          | 425 Comment: Formatting in Section 6.1 of Volume 3                |          |

|          | 426 Comments: Volume 2                                            |          |

|          | 427 Comment: Volume 3, Section 6                                  |          |

|          | 433 Editorial issues in PI 1.2 draft                              |          |

| 1.2      | 271 Support For Large Firmware Files And Firmware File Sections   | 01/19/09 |

|          | 284 CPU I/O protocol update                                       |          |

|          | 286 Legacy Region protocol                                        |          |

|          | 289 Recovery API                                                  |          |

|          | 292 PCD Specification Update                                      |          |

|          | 354 ACPI Manipulation Protocol                                    |          |

|          | 355 EFI_SIO_PROTOCOL Errata                                       |          |

|          | 365 UEFI Capsule HOB                                              |          |

|          | 382 IDE Controller Specification                                  |          |

|          | 385 Report Status Code Router Specification                       |          |

|          | 386 Status Code Specification                                     |          |

| Revision   | Mantis ID / Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2 errata | <ul> <li>345 Pl1.0 errata</li> <li>468 Issues on proposed Pl1.2 ACPI System Description Table Protocol</li> <li>492 Add Resource HOB Protectability Attributes</li> <li>494 Vol. 2 Appendix A Clean up</li> <li>495 Vol 1: update HOB reference</li> <li>380 Pl1.1 errata from SMM development</li> <li>501 Clean Up SetMemoryAttributes() language Per Mantis 489 (from USWG)</li> <li>502 Disk info</li> <li>503 typo</li> <li>504 remove support for fixed address resources</li> <li>509 PCI errata – execution phase</li> <li>510 PCI errata - platform policy</li> <li>511 PIC TE Image clarification/errata</li> <li>520 PI Errata</li> <li>521Add help text for EFI_PCD_PROTOCOL for GetNextTokenSpace</li> <li>525 Itanium ESAL, MCA/INIT/PMI errata</li> <li>526 PI SMM errata</li> <li>529 PCD issues in Volume 3 of the Pl1.2 Specification</li> <li>541 Volume 5 Typo</li> <li>543 Clarification around usage of FV Extended header</li> <li>550 Naming conflicts w/ PI SMM</li> </ul> | 12/16/09 |

| 1.1 Errata | <ul> <li>247 Clarification regarding use of dependency expression section types with firmware volume image files</li> <li>399 SMBIOS Protocol Errata</li> <li>405 PIWG Volume 5 incorrectly refers to EFI_PCI_OVERRIDE_PROTOCOL</li> <li>422 TEMPORARY_RAM_SUPPORT_PPI is misnamed</li> <li>428 Volume 5 PCI issue</li> <li>430 Clarify behavior w/ the FV extended header</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 02/23/09 |

| Revision           | Mantis ID / Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date                 |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.1 Errata         | 204 Stack HOB update 1.1errata     225 Correct references from EFI_FIRMWARE_VOLUME_PROTOCOL to EFI_FIRMWARE_VOLUME2_PROTOCOL     226 Remove references to Framework     227 Correct protocol name GUIDED_SECTION_EXTRACTION_PROTOCOL     228 insert"typedef" missing from some typedefs in Volume 3     243 Define interface "EFI_PEI_FV_PPI" declaration in PI1.0 FfsFindNextVolume()     285 Time quality of service in S3 boot script poll operation     287 Correct MP spec, PIVOLUME 2:Chapter 13.3 and 13.4 - return error language     290 PI Errata     305 Remove Datahub reference     336 SMM Control Protocol update     345 PI Errata     353 PI Errata     360 S3RestoreConfig description is missing     363 PI Volume 1 Errata     367 PCI Hot Plug Init errata     369 Volume 4 Errata     380 SMM Development errata     381 Errata on EFI_SMM_SAVE_STATE_IO_INFO | 01/13/09             |

| 1.1 Errata         | Revises typographical errors and minor omissionssee Errata for details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 04/25/08             |

| 1.1 correction 1.1 | Restore (missing) MP protocol  Mantis tickets:  M39 (Updates PCI Hostbridge & PCI Platform)  M41 (Duplicate 167)  M42 Add the definition of theDXE CIS Capsule AP & Variable AP  M43 (SMbios)  M46 (SMM error codes)  M163 (Add Volume 4SMM  M167 (Vol2: adds the DXE Boot Services Protocolsnew Chapter 12)  M179 (S3 boot script)  M180 (PMI ECR)  M195 (Remove PMI references from SMM CIS)  M196 (disposable-section type to the FFS)                                                                                                                                                                                                                                                                                                                                                                                                                                           | 03/12/08<br>11/05/07 |

| Revision   | Mantis ID / Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Date     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.0 errata | <ul> <li>Mantis tickets:</li> <li>M47 dxe_dispatcher_load_image_behavior</li> <li>M48 Make spec more consistent GUID &amp; filename.</li> <li>M155 FV_FILE and FV_ONLY: Change subtype number back to the original one.</li> <li>M171Remove 10 us lower bound restriction for the TickPeriod in the Metronome</li> <li>M178 Remove references to tail in file header and made file checksum for the data</li> <li>M183 Vol 1-Vol 5: Make spec more consistent.</li> <li>M192 Change PAD files to have an undefined GUID file name and update all FV</li> </ul> | 10/29/07 |

| 1.0        | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8/21/06  |

#### **Specification Volumes**

The **Platform Initialization Specification** is divided into volumes to enable logical organization, future growth, and printing convenience. The **Platform Initialization Specification** consists of the following volumes:

Volume 1: Pre-EFI Initialization Core Interface

**Volume 2: Driver Execution Environment Core Interface**

**Volume 3: Shared Architectural Elements**

Volume 4: System Management Mode

Volume 5: Standards

Each volume should be viewed in the context of all other volumes, and readers are strongly encouraged to consult the entire specification when researching areas of interest. Additionally, a single-file version of the **Platform Initialization Specification** is available to aid search functions through the entire specification.

### **Table of Contents**

| R  | evision History                            | iii |

|----|--------------------------------------------|-----|

|    | able of Contents                           |     |

| Li | st of Figures                              | xxi |

|    | st of Tables                               |     |

|    |                                            |     |

| 1  | Introduction                               |     |

|    | 1.1 Overview                               |     |

|    | 1.2 Organization of the PEI CIS            |     |

|    | 1.3 Conventions Used in this Document      |     |

|    | 1.3.1 Data Structure Descriptions          |     |

|    | 1.3.3 Instruction Descriptions             |     |

|    | 1.3.4 PPI Descriptions                     |     |

|    | 1.3.5 Pseudo-Code Conventions              |     |

|    | 1.3.6 Typographic Conventions              |     |

|    | 1.4 Requirements                           |     |

|    | 1.5 Conventions used in this document      | 6   |

|    | 1.5.1 Number formats                       |     |

|    | 1.5.2 Binary prefixes                      | 6   |

| 2  | Overview                                   | Q   |

| _  | 2.1 Introduction                           | _   |

|    | 2.2 Design Goals                           |     |

|    | 2.3 Pre-EFI Initialization (PEI) Phase     |     |

|    | 2.4 PEI Services                           |     |

|    | 2.5 PEI Foundation                         |     |

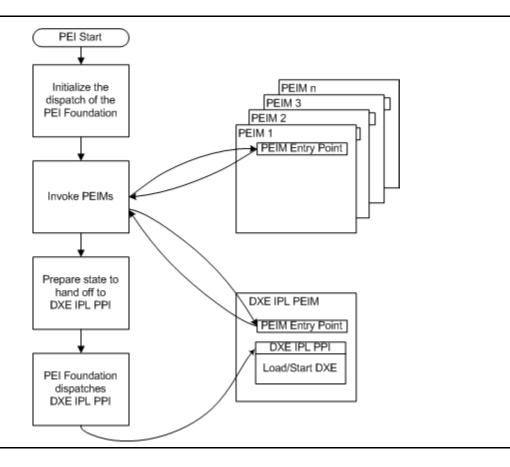

|    | 2.6 PEI Dispatcher                         | 11  |

|    | 2.7 Pre-EFI Initialization Modules (PEIMs) | 12  |

|    | 2.8 PEIM-to-PEIM Interfaces (PPIs)         |     |

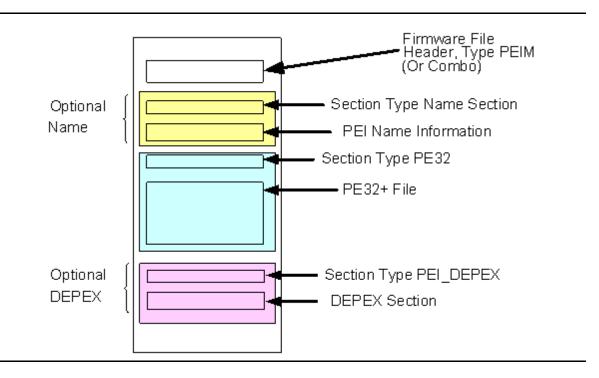

|    | 2.9 Firmware Volumes                       | 13  |

| 3  | PEI Services Table                         | 14  |

|    | 3.1 Introduction                           |     |

|    | 3.2 PEI Services Table                     |     |

|    | 3.2.1 EFI_PEI_SERVICES                     | 14  |

| 4  | Services - PEI                             | 20  |

| •  | 4.1 Introduction                           |     |

|    | 4.2 PPI Services                           |     |

|    | InstallPpi()                               |     |

|    | ReinstallPpi()                             |     |

|    | LocatePpi()                                |     |

|    | NotifyPpi()                                |     |

|    | 4.3 Boot Mode Services                     | 25  |

|   | GetBootMode()                                       | 26 |

|---|-----------------------------------------------------|----|

|   | SetBootMode()                                       |    |

|   | 4.4 HOB Services                                    | 28 |

|   | GetHobList()                                        | 29 |

|   | CreateHob()                                         | 30 |

|   | 4.5 Firmware Volume Services                        |    |

|   | FfsFindNextVolume()                                 | 32 |

|   | FfsFindNextFile()                                   | 33 |

|   | FfsFindSectionData()                                | 35 |

|   | FfsFindSectionData3()                               |    |

|   | FfsFindFileByName()                                 |    |

|   | FfsGetFileInfo()                                    | 39 |

|   | FfsGetFileInfo2()                                   | 41 |

|   | FfsGetVolumeInfo()                                  |    |

|   | RegisterForShadow()                                 |    |

|   | 4.6 PEI Memory Services                             | 45 |

|   | InstallPeiMemory()                                  |    |

|   | AllocatePages()                                     |    |

|   | AllocatePool()                                      |    |

|   | CopyMem()                                           |    |

|   | FreePages()                                         |    |

|   | SetMem()                                            |    |

|   | 4.7 Status Code Service                             |    |

|   | ReportStatusCode()                                  |    |

|   | 4.8 Reset Services                                  |    |

|   | ResetSystem()                                       |    |

|   | 4.9 I/O and PCI Services                            | 57 |

| 5 | PEI Foundation                                      | 58 |

|   | 5.1 Introduction                                    |    |

|   | 5.1.1 Prerequisites                                 |    |

|   | 5.1.2 Processor Execution Mode                      |    |

|   | 5.2 PEI Foundation Entry Point                      |    |

|   | 5.2.1 PEI Foundation Entry Point                    |    |

|   | 5.3 PEI Calling Convention Processor Binding        |    |

|   | 5.4 PEI Services Table Retrieval                    | 63 |

|   | 5.4.1 X86                                           |    |

|   | 5.4.2 x64                                           |    |

|   | 5.4.3 Itanium Processor Family – Register Mechanism |    |

|   | 5.4.4 ARM Processor Family – Register Mechanism     |    |

|   | 5.4.5 AArch64 Processor Family – Register Mechanism |    |

|   | 5.4.6 RISC-V Processor Family – Register Mechanism  |    |

|   | 5.5 PEI Dispatcher Introduction                     |    |

|   | 5.6 Ordering                                        |    |

|   | 5.6.1 Requirements                                  |    |

|   | 5.6.2 Requirement Representation and Notation       |    |

|   | 5.6.3 PEI a priori File Overview                    |    |

|   |                                                     |    |

|   | PEI_APRIORI_FILE_NAME_GUID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 5.6.4 Firmware Volume Image Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

|   | 5.6.5 PEIM Dependency Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

|   | 5.6.6 Types of Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |

|   | 5.7 Dependency Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|   | 5.7.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|   | PUSH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

|   | AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

|   | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|   | NOTTRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

|   | FALSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

|   | END                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

|   | 5.7.2 Dependency Expression with No Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

|   | 5.7.3 Empty Dependency Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|   | 5.7.4 Dependency Expression Reverse Polish Notation (RPN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

|   | 5.8 Dispatch Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|   | 5.8.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

|   | 5.8.2 Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|   | 5.8.3 Example Dispatch Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

|   | 5.8.4 Dispatching When Memory Exists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

|   | 5.8.5 PEIM Dispatching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85                         |

|   | 5.8.6 PEIM Authentication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85                         |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

| 6 | Architectural PPIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86                         |

| 6 | Architectural PPIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| 6 | 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86                         |

| 6 | 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86<br>86                   |

| 6 | 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86<br>86                   |

| 6 | 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86<br>86<br>86<br>87       |

| 6 | 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86<br>86<br>86<br>87       |

| 6 | 6.1 Introduction 6.2 Required Architectural PPIs 6.2.1 Master Boot Mode PPI (Required) EFI_PEI_MASTER_BOOT_MODE_PPI (Required) 6.2.2 DXE IPL PPI (Required) EFI_DXE_IPL_PPI (Required) EFI_DXE_IPL_PPI.Entry()                                                                                                                                                                                                                                                                                                                                                                                                                            | 86<br>86<br>86<br>87<br>87 |

| 6 | 6.1 Introduction  6.2 Required Architectural PPIs  6.2.1 Master Boot Mode PPI (Required)  EFI_PEI_MASTER_BOOT_MODE_PPI (Required)  6.2.2 DXE IPL PPI (Required)  EFI_DXE_IPL_PPI (Required)  EFI_DXE_IPL_PPI.Entry()  6.2.3 Memory Discovered PPI (Required)                                                                                                                                                                                                                                                                                                                                                                              | 86 86 86 87 87 88          |

| 6 | 6.1 Introduction 6.2 Required Architectural PPIs 6.2.1 Master Boot Mode PPI (Required) EFI_PEI_MASTER_BOOT_MODE_PPI (Required) 6.2.2 DXE IPL PPI (Required) EFI_DXE_IPL_PPI (Required) EFI_DXE_IPL_PPI.Entry() 6.2.3 Memory Discovered PPI (Required) EFI_PEI_PERMANENT_MEMORY_INSTALLED_PPI (Required)                                                                                                                                                                                                                                                                                                                                   | 86 86 86 87 87 87 87       |

| 6 | 6.1 Introduction 6.2 Required Architectural PPIs 6.2.1 Master Boot Mode PPI (Required) EFI_PEI_MASTER_BOOT_MODE_PPI (Required) 6.2.2 DXE IPL PPI (Required) EFI_DXE_IPL_PPI (Required) EFI_DXE_IPL_PPI.Entry() 6.2.3 Memory Discovered PPI (Required) EFI_PEI_PERMANENT_MEMORY_INSTALLED_PPI (Required) 6.3 Optional Architectural PPIs                                                                                                                                                                                                                                                                                                   | 86 86 86 87 87 87 90 90    |

| 6 | 6.1 Introduction 6.2 Required Architectural PPIs 6.2.1 Master Boot Mode PPI (Required) EFI_PEI_MASTER_BOOT_MODE_PPI (Required) 6.2.2 DXE IPL PPI (Required) EFI_DXE_IPL_PPI (Required) EFI_DXE_IPL_PPI.Entry() 6.2.3 Memory Discovered PPI (Required) EFI_PEI_PERMANENT_MEMORY_INSTALLED_PPI (Required) 6.3 Optional Architectural PPIs 6.3.1 Boot in Recovery Mode PPI (Optional)                                                                                                                                                                                                                                                        | 86 86 86 87 87 88 90 90    |

| 6 | 6.1 Introduction 6.2 Required Architectural PPIs 6.2.1 Master Boot Mode PPI (Required) EFI_PEI_MASTER_BOOT_MODE_PPI (Required) 6.2.2 DXE IPL PPI (Required) EFI_DXE_IPL_PPI (Required) EFI_DXE_IPL_PPI.Entry() 6.2.3 Memory Discovered PPI (Required) EFI_PEI_PERMANENT_MEMORY_INSTALLED_PPI (Required) 6.3 Optional Architectural PPIs 6.3.1 Boot in Recovery Mode PPI (Optional) EFI_PEI_BOOT_IN_RECOVERY_MODE_PPI (Optional)                                                                                                                                                                                                           | 86 86 86 87 88 90 91 91    |

| 6 | 6.1 Introduction 6.2 Required Architectural PPIs 6.2.1 Master Boot Mode PPI (Required) EFI_PEI_MASTER_BOOT_MODE_PPI (Required) 6.2.2 DXE IPL PPI (Required) EFI_DXE_IPL_PPI (Required) EFI_DXE_IPL_PPI.Entry() 6.2.3 Memory Discovered PPI (Required) EFI_PEI_PERMANENT_MEMORY_INSTALLED_PPI (Required) 6.3 Optional Architectural PPIs 6.3.1 Boot in Recovery Mode PPI (Optional) EFI_PEI_BOOT_IN_RECOVERY_MODE_PPI (Optional) 6.3.2 End of PEI Phase PPI (Optional)                                                                                                                                                                     | 86 86 86 87 87 87 90 91 91 |

| 6 | 6.1 Introduction 6.2 Required Architectural PPIs 6.2.1 Master Boot Mode PPI (Required) EFI_PEI_MASTER_BOOT_MODE_PPI (Required) 6.2.2 DXE IPL PPI (Required) EFI_DXE_IPL_PPI (Required) EFI_DXE_IPL_PPI.Entry(). 6.2.3 Memory Discovered PPI (Required) EFI_PEI_PERMANENT_MEMORY_INSTALLED_PPI (Required) 6.3 Optional Architectural PPIs 6.3.1 Boot in Recovery Mode PPI (Optional) EFI_PEI_BOOT_IN_RECOVERY_MODE_PPI (Optional) 6.3.2 End of PEI Phase PPI (Optional) EFI_PEI_END_OF_PEI_PHASE_PPI (Optional)                                                                                                                            |                            |