12.6. Interrupt Model¶

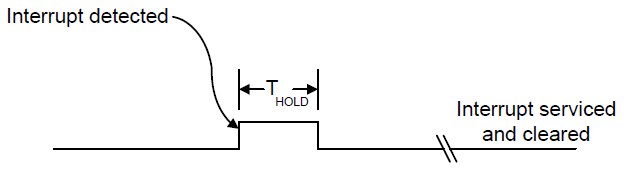

The EC Interrupt Model uses pulsed interrupts to speed the clearing process. The Interrupt is firmware generated using an EC general-purpose output and has the waveform shown in Interrupt Model . The embedded controller SCI is always wired directly to a GPE input or a GPIO pin, and OSPM driver treats this as an edge event (the EC SCI cannot be shared).

Fig. 12.3 Interrupt Model¶

12.6.1. Event Interrupt Model¶

The embedded controller must generate SCIs for the events listed in the following table.

Event |

Description |

|---|---|

IBF=0 |

Signals that the embedded controller has read the last command or data from the input buffer and the host is free to send more data. |

OBF=1 |

Signals that the embedded controller has written a byte of data into the output buffer and the host is free to read the returned data. |

SCI_EVT=1 |

Signals that the embedded controller has detected an event that requires OS attention. OSPM should issue a query (QR_EC) command to find the cause of the event. |

12.6.2. Command Interrupt Model¶

The embedded controller must generate SCIs for commands as follows:

Byte #1 |

(Command byte Header) |

Interrupt on IBF=0 |

Byte #2 |

(Address byte to read) |

No Interrupt |

Byte #3 |

(Data read to host) |

Interrupt on OBF=1 |

Byte #1 |

(Command byte Header) |

Interrupt on IBF=0 |

Byte #2 |

(Address byte to write) |

Interrupt on IBF=0 |

Byte #3 |

(Data to read ) |

Interrupt on IBF=0 |

Byte #1 |

(Command byte Header) |

No Interrupt |

Byte #2 |

(Query value to host) |

Interrupt on OBF=1 |

Byte #1 |

(Command byte Header) |

No Interrupt |

Byte #2 |

(Burst acknowledge byte) |

Interrupt on OBF=1 |

Byte #1 |

(Command byte Header) |

Interrupt on IBF=0 |